SCPS201A -AUGUST 2009-REVISED SEPTEMBER 2009

# LOW VOLTAGE 16-BIT I<sup>2</sup>C AND SMBus LOW-POWER I/O EXPANDER WITH INTERRUPT OUTPUT AND CONFIGURATION REGISTERS

Check for Samples: TCA9535

#### **FEATURES**

- Low Standby-Current Consumption of 3 µA Max

- I<sup>2</sup>C to Parallel Port Expander

- Open-Drain Active-Low Interrupt Output

- 5-V Tolerant I/O Ports

- Compatible With Most Microcontrollers

- 400-kHz Fast I<sup>2</sup>C Bus

- · Polarity Inversion Register

- Address by Three Hardware Address Pins for Use of up to Eight Devices

- Latched Outputs With High-Current Drive Capability for Directly Driving LEDs

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 1000-V Charged-Device Model (C101)

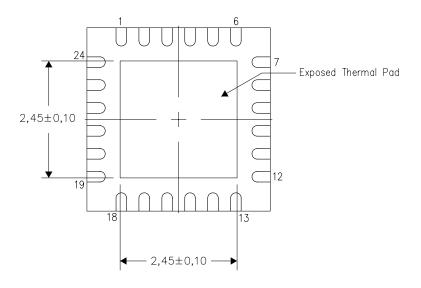

The exposed center pad, if used, must be connected as a secondary ground or left electrically open.

### **DESCRIPTION/ORDERING INFORMATION**

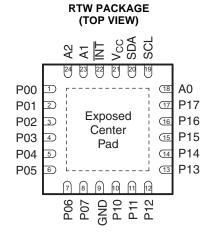

This 16-bit I/O expander for the two-line bidirectional bus ( $I^2C$ ) is designed for 1.65-V to 5.5-V V<sub>CC</sub> operation. It provides general-purpose remote I/O expansion for most microcontroller families via the  $I^2C$  interface [serial clock (SCL), serial data (SDA)].

The TCA9535 consists of two 8-bit Configuration (input or output selection), Input Port, Output Port, and Polarity Inversion (active-high or active-low operation) registers. At power on, the I/Os are configured as inputs. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding Input or Output Port register. The polarity of the Input Port register can be inverted with the Polarity Inversion register. All registers can be read by the system master.

The system master can reset the TCA9535 in the event of a timeout or other improper operation by utilizing the power-on reset feature, which puts the registers in their default state and initializes the I<sup>2</sup>C/SMBus state machine.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **DESCRIPTION/ORDERING INFORMATION (CONTINUED)**

The TCA9535 open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed.

INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C bus. Thus, the TCA9535 can remain a simple slave device.

The device outputs (latched) have high-current drive capability for directly driving LEDs. The device has low current consumption.

Although pin-to-pin and I<sup>2</sup>C address compatible with the PCF8575, software changes are required due to the enhancements.

The TCA9535 is identical to the PCA9555, except for the removal of the internal I/O pullup resistor, which greatly reduces power consumption when the I/Os are held low.

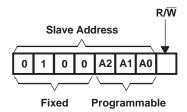

Three hardware pins (A0, A1, and A2) are used to program and vary the fixed I<sup>2</sup>C address and allow up to eight devices to share the same I<sup>2</sup>C bus or SMBus. The fixed I<sup>2</sup>C address of the TCA9535 is the same as the PCA9555, PCF8575C, and PCF8574, allowing up to eight of these devices in any combination to share the same I<sup>2</sup>C bus or SMBus.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKA      | GE <sup>(1)</sup> (2) | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------|-----------------------|-----------------------|------------------|

| –40°C to 85°C  | TSSOP – PW | Reel of 2000          | TCA9535PWR            | PW535            |

|                | QFN – RTW  | Reel of 3000          | TCA9535RTWR           | PW535            |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

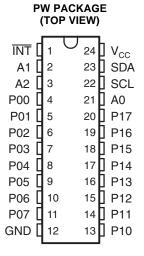

## **TERMINAL FUNCTIONS**

|               | NO.         |              |                 |                                                                                              |

|---------------|-------------|--------------|-----------------|----------------------------------------------------------------------------------------------|

| TSSOP<br>(PW) | QFN<br>RTW) | BGA<br>(ZQS) | NAME            | DESCRIPTION                                                                                  |

| 1             | 22          | А3           | ĪNT             | Interrupt output. Connect to V <sub>CC</sub> through a pullup resistor.                      |

| 2             | 23          | В3           | A1              | Address input. Connect directly to V <sub>CC</sub> or ground.                                |

| 3             | 24          | A2           | A2              | Address input. Connect directly to V <sub>CC</sub> or ground.                                |

| 4             | 1           | A1           | P00             | P-port input/output. Push-pull design structure. At power-on, P00 is configured as an input. |

| 5             | 2           | C3           | P01             | P-port input/output. Push-pull design structure. At power-on, P01 is configured as an input. |

| 6             | 3           | B1           | P02             | P-port input/output. Push-pull design structure. At power-on, P02 is configured as an input. |

| 7             | 4           | C1           | P03             | P-port input/output. Push-pull design structure. At power-on, P03 is configured as an input. |

| 8             | 5           | C2           | P04             | P-port input/output. Push-pull design structure. At power-on, P04 is configured as an input. |

| 9             | 6           | D1           | P05             | P-port input/output. Push-pull design structure. At power-on, P05 is configured as an input. |

| 10            | 7           | E1           | P06             | P-port input/output. Push-pull design structure. At power-on, P06 is configured as an input. |

| 11            | 8           | D2           | P07             | P-port input/output. Push-pull design structure. At power-on, P07 is configured as an input. |

| 12            | 9           | E2           | GND             | Ground                                                                                       |

| 13            | 10          | E3           | P10             | P-port input/output. Push-pull design structure. At power-on, P10 is configured as an input. |

| 14            | 11          | E4           | P11             | P-port input/output. Push-pull design structure. At power-on, P11 is configured as an input. |

| 15            | 12          | D3           | P12             | P-port input/output. Push-pull design structure. At power-on, P12 is configured as an input. |

| 16            | 13          | E5           | P13             | P-port input/output. Push-pull design structure. At power-on, P13 is configured as an input. |

| 17            | 14          | D4           | P14             | P-port input/output. Push-pull design structure. At power-on, P14 is configured as an input. |

| 18            | 15          | D5           | P15             | P-port input/output. Push-pull design structure. At power-on, P15 is configured as an input. |

| 19            | 16          | C5           | P16             | P-port input/output. Push-pull design structure. At power-on, P16 is configured as an input. |

| 20            | 17          | C4           | P17             | P-port input/output. Push-pull design structure. At power-on, P17 is configured as an input. |

| 21            | 18          | B5           | A0              | Address input. Connect directly to V <sub>CC</sub> or ground.                                |

| 22            | 19          | A5           | SCL             | Serial clock bus. Connect to V <sub>CC</sub> through a pullup resistor.                      |

| 23            | 20          | A4           | SDA             | Serial data bus. Connect to V <sub>CC</sub> through a pullup resistor.                       |

| 24            | 21          | B4           | V <sub>CC</sub> | Supply voltage                                                                               |

# LOGIC DIAGRAM (POSITIVE LOGIC)

- A. Pin numbers shown are for the PW package.

- B. All I/Os are set to inputs at reset.

**Data From Output Port Shift Register Register Data** Configuration  $v_{cc}$ Register Q1 **Data From Shift Register** FF D Q **Write Configuration** CLK Q FF **Pulse** I/O Pin Write Pulse -CLK Q **Output Port** Register Q2 **Input Port GND** Register **Input Port Register Data** FF Read Pulse -CLK Q To INT **Data From Polarity** D **Shift Register Register Data** FF Write Polarity CLK Q Pulse **Polarity Inversion** Register

Figure 1. SIMPLIFIED SCHEMATIC OF P-PORT I/Os

(1) At power-on reset, all registers return to default values.

## I/O Port

When an I/O is configured as an input, FETs Q1 and Q2 are off, which creates a high-impedance input. The input voltage may be raised above  $V_{CC}$  to a maximum of 5.5 V.

If the I/O is configured as an output, Q1 or Q2 is enabled, depending on the state of the Output Port register. In this case, there are low-impedance paths between the I/O pin and either  $V_{CC}$  or GND. The external voltage applied to this I/O pin should not exceed the recommended levels for proper operation.

Copyright © 2009, Texas Instruments Incorporated

#### I<sup>2</sup>C Interface

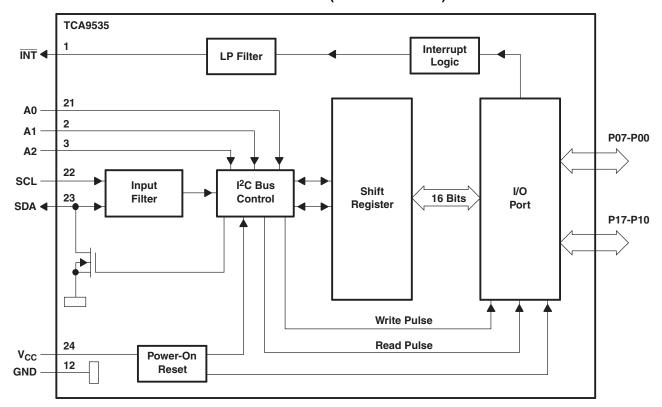

The bidirectional I<sup>2</sup>C bus consists of the serial clock (SCL) and serial data (SDA) lines. Both lines must be connected to a positive supply via a pullup resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

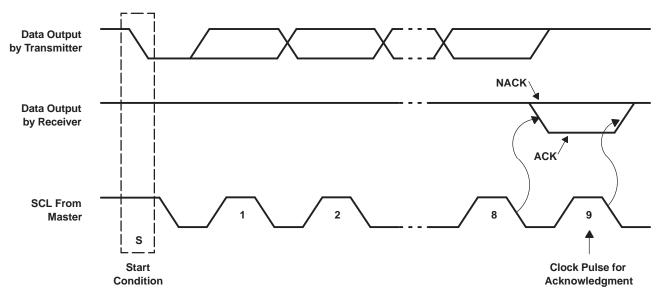

$I^2C$  communication with this device is initiated by a master sending a Start condition, a high-to-low transition on the SDA input/output while the SCL input is high (see Figure 2). After the Start condition, the device address byte is sent, MSB first, including the data direction bit (R/W). This device does not respond to the general call address.

After receiving the valid address byte, this device responds with an ACK, a low on the SDA input/output during the high of the ACK-related clock pulse. The address inputs (A0–A2) of the slave device must not be changed between the Start and Stop conditions.

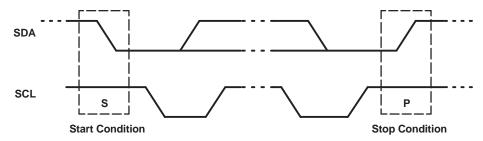

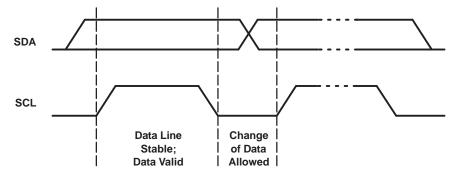

On the I<sup>2</sup>C bus, only one data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high pulse of the clock period, as changes in the data line at this time are interpreted as control commands (Start or Stop) (see Figure 3).

A Stop condition, a low-to-high transition on the SDA input/output while the SCL input is high, is sent by the master (see Figure 2).

Any number of data bytes can be transferred from the transmitter to the receiver between the Start and the Stop conditions. Each byte of eight bits is followed by one ACK bit. The transmitter must release the SDA line before the receiver can send an ACK bit. The device that acknowledges must pull down the SDA line during the ACK clock pulse so that the SDA line is stable low during the high pulse of the ACK-related clock period (see Figure 4). When a slave receiver is addressed, it must generate an ACK after each byte is received. Similarly, the master must generate an ACK after each byte that it receives from the slave transmitter. Setup and hold times must be met to ensure proper operation.

A master receiver signals an end of data to the slave transmitter by not generating an acknowledge (NACK) after the last byte has been clocked out of the slave. This is done by the master receiver by holding the SDA line high. In this event, the transmitter must release the data line to enable the master to generate a Stop condition.

Figure 2. Definition of Start and Stop Conditions

Figure 3. Bit Transfer

Figure 4. Acknowledgment on I<sup>2</sup>C Bus

**Table 1. Interface Definition**

| ВҮТЕ                           |         | BIT |     |     |     |     |     |         |  |  |  |

|--------------------------------|---------|-----|-----|-----|-----|-----|-----|---------|--|--|--|

|                                | 7 (MSB) | 6   | 5   | 4   | 3   | 2   | 1   | 0 (LSB) |  |  |  |

| I <sup>2</sup> C slave address | L       | Н   | L   | L   | A2  | A1  | A0  | R/W     |  |  |  |

| P0x I/O data bus               | P07     | P06 | P05 | P04 | P03 | P02 | P01 | P00     |  |  |  |

| P1x I/O data bus               | P17     | P16 | P15 | P14 | P13 | P12 | P11 | P10     |  |  |  |

#### **Device Address**

Figure 5 shows the address byte of the TCA9535.

Figure 5. TCA9535 Address

Table 2. Address Reference

|    | INPUTS |    | I <sup>2</sup> C BUS SLAVE ADDRESS |

|----|--------|----|------------------------------------|

| A2 | A1     | A0 | IC BUS SLAVE ADDRESS               |

| L  | L      | L  | 32 (decimal), 20 (hexadecimal)     |

| L  | L      | Н  | 33 (decimal), 21 (hexadecimal)     |

| L  | Н      | L  | 34 (decimal), 22 (hexadecimal)     |

| L  | Н      | Н  | 35 (decimal), 23 (hexadecimal)     |

| Н  | L      | L  | 36 (decimal), 24 (hexadecimal)     |

| Н  | L      | Н  | 37 (decimal), 25 (hexadecimal)     |

| Н  | Н      | L  | 38 (decimal), 26 (hexadecimal)     |

| Н  | Н      | Н  | 39 (decimal), 27 (hexadecimal)     |

The last bit of the slave address defines the operation (read or write) to be performed. A high (1) selects a read operation, while a low (0) selects a write operation.

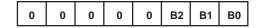

#### **Control Register and Command Byte**

Following the successful acknowledgment of the address byte, the bus master sends a command byte that is stored in the control register in the TCA9535. Three bits of this data byte state the operation (read or write) and the internal register (Input, Output, Polarity Inversion, or Configuration) that will be affected. This register can be written or read through the I<sup>2</sup>C bus. The command byte is sent only during a write transmission.

Once a command byte has been sent, the register that was addressed continues to be accessed by reads until a new command byte has been sent.

Figure 6. Control Register Bits

**Table 3. Control Register**

| CONTR | OL REGIST | ER BITS | COMMAND    | REGISTER                             | PROTOCOL                             | POWER-UP  |

|-------|-----------|---------|------------|--------------------------------------|--------------------------------------|-----------|

| B2    | B1        | В0      | BYTE (HEX) | REGISTER                             | PROTOCOL                             | DEFAULT   |

| 0     | 0         | 0       | 0x00       | Input Port 0                         | Read byte                            | xxxx xxxx |

| 0     | 0         | 1       | 0x01       | Input Port 1                         | Read byte                            | xxxx xxxx |

| 0     | 1         | 0       | 0x02       | Output Port 0                        | 0 Read/Write byte                    |           |

| 0     | 1         | 1       | 0x03       | Output Port 1                        | Read/Write byte                      | 1111 1111 |

| 1     | 0         | 0       | 0x04       | Polarity Inversion Port 0            | Read/Write byte                      | 0000 0000 |

| 1     | 0         | 1       | 0x05       | Polarity Inversion Port 1            | Read/Write byte                      | 0000 0000 |

| 1     | 1         | 0       | 0x06       | Configuration Port 0 Read/Write byte |                                      | 1111 1111 |

| 1     | 1         | 1       | 0x07       | Configuration Port 1                 | Configuration Port 1 Read/Write byte |           |

#### **Register Descriptions**

The Input Port registers (registers 0 and 1) reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the Configuration Register. It only acts on read operation. Writes to these registers have no effect. The default value, X, is determined by the externally applied logic level.

Before a read operation, a write transmission is sent with the command byte to let the I<sup>2</sup>C device know that the Input Port registers will be accessed next.

Table 4. Registers 0 and 1 (Input Port Registers)

| Bit     | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | Х    | Х    | Х    | Х    | X    | Х    | X    | Х    |

| Bit     | I1.7 | I1.6 | I1.5 | I1.4 | I1.3 | l1.2 | l1.1 | I1.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

The Output Port registers (registers 2 and 3) show the outgoing logic levels of the pins defined as outputs by the Configuration register. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 5. Registers 2 and 3 (Output Port Registers)

| Bit     | 00.7 | O0.6 | O0.5 | 00.4 | 00.3 | 00.2 | 00.1 | 00.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Bit     | 01.7 | 01.6 | 01.5 | 01.4 | 01.3 | 01.2 | 01.1 | 01.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

The Polarity Inversion registers (registers 4 and 5) allow polarity inversion of pins defined as inputs by the Configuration register. If a bit in this register is set (written with 1), the corresponding pin's polarity is inverted. If a bit in this register is cleared (written with a 0), the corresponding pin's original polarity is retained.

Table 6. Registers 4 and 5 (Polarity Inversion Registers)

| Bit     | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Bit     | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

The Configuration registers (registers 6 and 7) configure the directions of the I/O pins. If a bit in this register is set to 1, the corresponding port pin is enabled as an input with a high-impedance output driver. If a bit in this register is cleared to 0, the corresponding port pin is enabled as an output.

Table 7. Registers 6 and 7 (Configuration Registers)

| Bit     | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Bit     | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### **Power-On Reset**

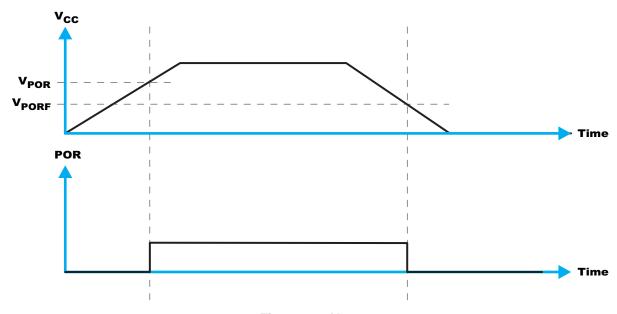

When power (from 0 V) is applied to  $V_{CC}$ , an internal power-on reset holds the TCA9535 in a reset condition until  $V_{CC}$  has reached  $V_{POR}$ . At that point, the reset condition is released, and the TCA9535 registers and  $I^2C/SMBus$  state machine initialize to their default states. After that,  $V_{CC}$  must be lowered to below 0.2 V and then back up to the operating voltage for a power-reset cycle.

## Interrupt (INT) Output

An interrupt is generated by any rising or falling edge of the port inputs in the input mode. After time,  $t_{iv}$ , the signal  $\overline{INT}$  is valid. Resetting the interrupt circuit is achieved when data on the port is changed to the original setting or data is read from the port that generated the interrupt. Resetting occurs in the read mode at the acknowledge (ACK) bit or not acknowledge (NACK) bit after the falling edge of the SCL signal. Interrupts that occur during the ACK or NACK clock pulse can be lost (or be very short) due to the resetting of the interrupt during this pulse. Each change of the I/Os after resetting is detected and is transmitted as  $\overline{INT}$ .

Reading from or writing to another device does not affect the interrupt circuit, and a pin configured as an output cannot cause an interrupt. Changing an I/O from an output to an input may cause a false interrupt to occur, if the state of the pin does not match the contents of the Input Port register. Because each 8-bit port is read independently, the interrupt caused by port 0 is not cleared by a read of port 1, or vice versa.

INT has an open-drain structure and requires a pullup resistor to V<sub>CC</sub>.

#### **Bus Transactions**

Data is exchanged between the master and the TCA9535 through write and read commands.

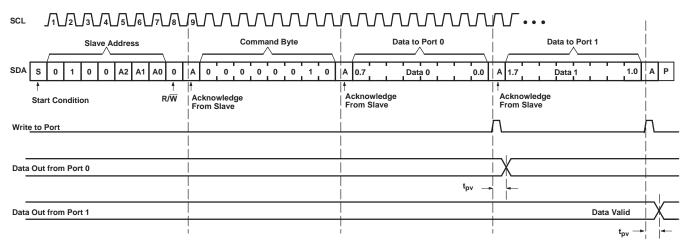

#### Writes

Data is transmitted to the TCA9535 by sending the device address and setting the least-significant bit to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register receives the data that follows the command byte.

The eight registers within the TCA9535 are configured to operate as four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversions, and Configurations. After sending data to one register, the next data byte is sent to the other register in the pair (see Figure 7 and Figure 8). For example, if the first byte is sent to Output Port 1 (register 3), the next byte is stored in Output Port 0 (register 2).

There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

Figure 7. Write to Output Port Registers

Figure 8. Write to Configuration Registers

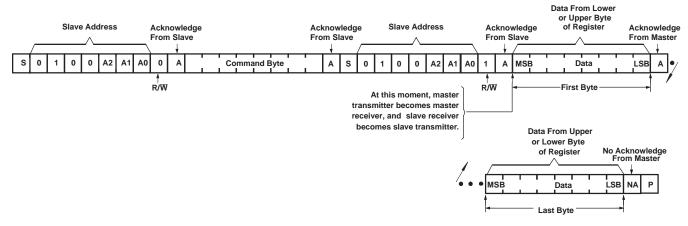

#### Reads

The bus master first must send the TCA9535 address with the least-significant bit set to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register is accessed. After a restart, the device address is sent again, but this time, the least-significant bit is set to a logic 1. Data from the register defined by the command byte then is sent by the TCA9535 (see Figure 9 through Figure 11).

After a restart, the value of the register defined by the command byte matches the register being accessed when the restart occurred. For example, if the command byte references Input Port 1 before the restart, and the restart occurs when Input Port 0 is being read, the stored command byte changes to reference Input Port 0. The original command byte is forgotten. If a subsequent restart occurs, Input Port 0 is read first. Data is clocked into the register on the rising edge of the ACK clock pulse. After the first byte is read, additional bytes may be read, but the data now reflect the information in the other register in the pair. For example, if Input Port 1 is read, the next byte read is Input Port 0.

Data is clocked into the register on the rising edge of the ACK clock pulse. There is no limitation on the number of data bytes received in one read transmission, but when the final byte is received, the bus master must not acknowledge the data

Figure 9. Read From Register

- A. Transfer of data can be stopped at any time by a Stop condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte previously has been set to 00 (read Input Port register).

- B. This figure eliminates the command byte transfer, a restart, and slave address call between the initial slave address call and actual data transfer from P port (see Figure 9 for these details).

Figure 10. Read Input Port Register, Scenario 1

- A. Transfer of data can be stopped at any time by a Stop condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte previously has been set to 00 (read Input Port register).

- B. This figure eliminates the command byte transfer, a restart, and slave address call between the initial slave address call and actual data transfer from P port (see Figure 9 for these details).

Figure 11. Read Input Port Register, Scenario 2

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                |                                                        | MIN  | MAX  | UNIT |

|------------------|----------------------------------------------------------------|--------------------------------------------------------|------|------|------|

| V <sub>CC</sub>  | Supply voltage range                                           |                                                        | -0.5 | 6    | V    |

| VI               | Input voltage range <sup>(2)</sup>                             |                                                        | -0.5 | 6    | V    |

| Vo               | Output voltage range <sup>(2)</sup>                            |                                                        | -0.5 | 6    | V    |

| I <sub>IK</sub>  | Input clamp current                                            | V <sub>I</sub> < 0                                     |      | -20  | mA   |

| I <sub>OK</sub>  | Output clamp current                                           | V <sub>0</sub> < 0                                     |      | -20  | mA   |

| I <sub>IOK</sub> | Input/output clamp current                                     | V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> |      | ±20  | mA   |

| I <sub>OL</sub>  | Continuous output low current                                  | $V_O = 0$ to $V_{CC}$                                  |      | 50   | mA   |

| I <sub>OH</sub>  | Continuous output high current                                 | $V_O = 0$ to $V_{CC}$                                  |      | -50  | mA   |

|                  | Continuous current through GND                                 |                                                        |      | -250 | 1    |

| Icc              | Continuous current through V <sub>CC</sub>                     |                                                        |      |      | mA   |

| ^                |                                                                | PW package                                             |      | 88   |      |

| $\theta_{JA}$    | Package thermal impedance, junction to free air <sup>(3)</sup> | RTW package                                            |      | 66   | °C/W |

| T <sub>stg</sub> | Storage temperature range                                      |                                                        | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                 |                                |                         | MIN                   | MAX                 | UNIT |  |

|-----------------|--------------------------------|-------------------------|-----------------------|---------------------|------|--|

| V <sub>CC</sub> | Supply voltage                 |                         | 1.65                  | 5.5                 | V    |  |

| V               | High lovel input valtage       | SCL, SDA                | 0.7 × V <sub>CC</sub> | 5.5                 | V    |  |

| $V_{IH}$        | High-level input voltage       | A2-A0, P07-P00, P17-P10 | 0.7 × V <sub>CC</sub> | 5.5                 | V    |  |

| .,              | Low lovel input voltage        | SCL, SDA                | -0.5                  | $0.3 \times V_{CC}$ | ;    |  |

| $V_{IL}$        | Low-level input voltage        | A2-A0, P07-P00, P17-P10 | -0.5                  | 5.5<br>5.5<br>5.5   | V    |  |

| I <sub>OH</sub> | High-level output current      | P07–P00, P17–P10        |                       | -10                 | mA   |  |

| I <sub>OL</sub> | Low-level output current       | P07-P00, P17-P10        |                       | 25                  | mA   |  |

| T <sub>A</sub>  | Operating free-air temperature |                         | -40                   | 85                  | °C   |  |

Product Folder Link(s): TCA9535

<sup>(2)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>(3)</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

### **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                       | TEST CONDITIONS                                                                 | V <sub>cc</sub>  | MIN  | TYP <sup>(1)</sup> | MAX                                                                    | UNIT |

|------------------|-------------------------------------------------|---------------------------------------------------------------------------------|------------------|------|--------------------|------------------------------------------------------------------------|------|

| V <sub>IK</sub>  | Input diode clamp voltage                       | I <sub>I</sub> = -18 mA                                                         | 1.65 V to 5.5 V  | -1.2 |                    |                                                                        | V    |

| $V_{POR}$        | Power-on reset voltage                          | $V_I = V_{CC}$ or GND, $I_O = 0$                                                | 1.65 V to 5.5 V  |      | 1.5                | 1.65                                                                   | V    |

|                  |                                                 |                                                                                 | 1.65 V           | 1.2  |                    |                                                                        |      |

|                  |                                                 |                                                                                 | 2.3 V            | 1.8  |                    |                                                                        |      |

|                  |                                                 | $I_{OH} = -8 \text{ mA}$                                                        | 3 V              | 2.6  |                    |                                                                        |      |

| .,               | December 1 to 1 t |                                                                                 | 4.75 V           | 4.1  |                    |                                                                        |      |

| $V_{OH}$         | P-port high-level output voltage <sup>(2)</sup> |                                                                                 | 1.65 V           | 1.8  |                    | ±1<br>±1<br>1<br>-1<br>200<br>75<br>50<br>45<br>1.5<br>1.3<br>1<br>0.9 | V    |

|                  |                                                 |                                                                                 | 2.3 V            | 1.7  |                    |                                                                        |      |

|                  |                                                 | $I_{OH} = -10 \text{ mA}$                                                       | 3 V              | 2.5  |                    |                                                                        |      |

|                  |                                                 |                                                                                 | 4.75 V           | 4    |                    |                                                                        |      |

|                  | SDA                                             | V <sub>OL</sub> = 0.4 V                                                         |                  | 3    |                    |                                                                        |      |

|                  | D = = (3)                                       | V <sub>OL</sub> = 0.5 V                                                         | 4.05.7/1- 5.5.7/ | 8    | 20                 |                                                                        | ^    |

| l <sub>OL</sub>  | P port <sup>(3)</sup>                           | V <sub>OL</sub> = 0.7 V                                                         | 1.65 V to 5.5 V  | 10   | 24                 |                                                                        | mA   |

|                  | ĪNT                                             | V <sub>OL</sub> = 0.4 V                                                         |                  | 3    |                    |                                                                        |      |

|                  | SCL, SDA                                        | V V OND                                                                         | 4.05.7/1- 5.5.7/ |      |                    | ±1                                                                     | ^    |

| II               | A2-A0                                           | $V_I = V_{CC}$ or GND                                                           | 1.65 V to 5.5 V  |      |                    | ±1                                                                     | μΑ   |

| I <sub>IH</sub>  | P port                                          | $V_I = V_{CC}$                                                                  | 1.65 V to 5.5 V  |      |                    | 1                                                                      | μA   |

| I <sub>IL</sub>  | P port                                          | V <sub>I</sub> = GND                                                            | 1.65 V to 5.5 V  |      |                    | -1                                                                     | μA   |

|                  |                                                 |                                                                                 | 5.5 V            |      | 100                | 200                                                                    |      |

|                  | On another was de-                              | $V_I = V_{CC}$ or GND, $I_O = 0$ ,                                              | 3.6 V            |      | 30                 | 75                                                                     |      |

|                  | Operating mode                                  | $I/O = inputs, f_{SCL} = 400 \text{ kHz}$                                       | 2.7 V            |      | 20                 | ±1 1 -1 200 75 50 45 1.5 1.3 1 0.9 1.5 7                               |      |

|                  |                                                 |                                                                                 | 1.95 V           |      | 10                 |                                                                        |      |

| I <sub>CC</sub>  |                                                 |                                                                                 | 5.5 V            |      | 1.1                | 1.5                                                                    | μΑ   |

|                  | Ota a discourse de                              | $V_I = GND$ , $I_O = 0$ , $I/O = inputs$ ,                                      | 3.6 V            |      | 0.7                | 1.3                                                                    |      |

|                  | Standby mode                                    | f <sub>SCL</sub> = 0 kHz                                                        | 2.7 V            |      | 0.5                | 1                                                                      |      |

|                  |                                                 |                                                                                 | 1.95 V           |      | 0.3                | 0.9                                                                    |      |

| ΔI <sub>CC</sub> | Additional current in standby mode              | One input at V <sub>CC</sub> – 0.6 V,<br>Other inputs at V <sub>CC</sub> or GND | 1.65 V to 5.5 V  |      |                    | 1.5                                                                    | mA   |

| Cı               | SCL                                             | V <sub>I</sub> = V <sub>CC</sub> or GND                                         | 1.65 V to 5.5 V  |      | 3                  | 7                                                                      | pF   |

| ^                | SDA                                             | V V == CND                                                                      | 4.05.7/4- 5.5.7/ |      | 3                  | 7                                                                      |      |

| $C_{io}$         | P port                                          | $V_{IO} = V_{CC}$ or GND                                                        | 1.65 V to 5.5 V  |      | 3.7                | 9.5                                                                    | pF   |

<sup>(1)</sup> All typical values are at nominal supply voltage (1.8-V, 2.5-V, 3.3-V, or 5-V V<sub>CC</sub>) and T<sub>A</sub> = 25°C.

(2) Each I/O must be limited externally to a maximum of 25 mA, and each octal (P07–P00 and P17–P10) must be limited to a maximum current of 100 mA, for a device total of 200 mA.

<sup>(3)</sup> The total current sourced by all I/Os must be limited to 160 mA (80 mA for P07–P00 and 80 mA for P17–P10).

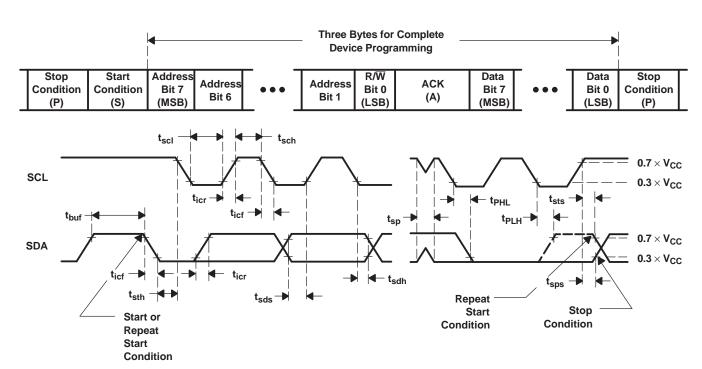

# I<sup>2</sup>C INTERFACE TIMING REQUIREMENTS

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 12)

|                       |                                                         |                                          | MIN               | MAX | UNIT |

|-----------------------|---------------------------------------------------------|------------------------------------------|-------------------|-----|------|

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                        |                                          | 0                 | 400 | kHz  |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time                        | 0.6                                      |                   | μs  |      |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time                         | 1.3                                      |                   | μs  |      |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                             |                                          | 50                | ns  |      |

| t <sub>sds</sub>      | I <sup>2</sup> C serial-data setup time                 | 100                                      |                   | ns  |      |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial-data hold time                  | 0                                        |                   | ns  |      |

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time                        | $20 + 0.1C_b$ (1)                        | 300               | ns  |      |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                        | 20 + 0.1C <sub>b</sub> <sup>(1)</sup>    | 300               | ns  |      |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time                       | 10-pF to 400-pF bus                      | $20 + 0.1C_b$ (1) | 300 | ns   |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between Stop and Sta     | rt                                       | 1.3               |     | μs   |

| t <sub>sts</sub>      | I <sup>2</sup> C Start or repeated Start condition setu | up                                       | 0.6               |     | μs   |

| t <sub>sth</sub>      | I <sup>2</sup> C Start or repeated Start condition hold | d                                        | 0.6               |     | μs   |

| t <sub>sps</sub>      | I <sup>2</sup> C Stop condition setup                   |                                          | 0.6               |     | μs   |

| t <sub>vd(data)</sub> | Valid-data time                                         | SCL low to SDA output valid              | 50                |     | ns   |

| t <sub>vd(ack)</sub>  | Valid-data time of ACK condition                        | ACK signal from SCL low to SDA (out) low | 0.1               | 0.9 | μs   |

| C <sub>b</sub>        | I <sup>2</sup> C bus capacitive load                    |                                          |                   | 400 | pF   |

<sup>(1)</sup> C<sub>b</sub> = total capacitance of one bus line in pF

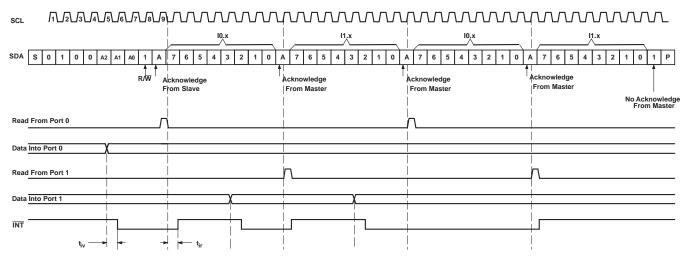

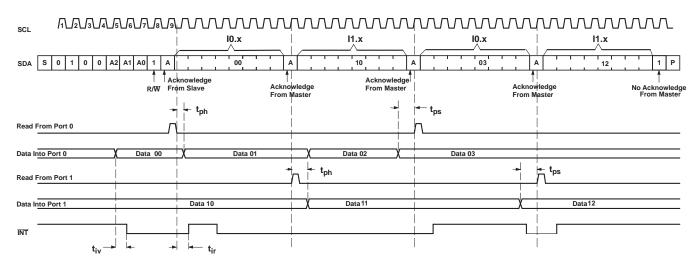

# **SWITCHING CHARACTERISTICS**

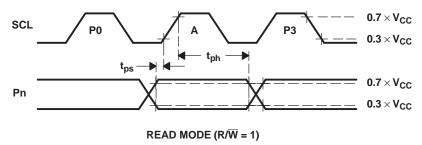

over recommended operating free-air temperature range,  $C_L \le 100 \text{ pF}$  (unless otherwise noted) (see Figure 13 and Figure 14)

| PARAMETER       |                            | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN | MAX | UNIT |

|-----------------|----------------------------|-----------------|----------------|-----|-----|------|

| t <sub>iv</sub> | Interrupt valid time       | P port          | ĪNT            |     | 4   | μs   |

| t <sub>ir</sub> | Interrupt reset delay time | SCL             | ĪNT            |     | 4   | μs   |

| t <sub>pv</sub> | Output data valid          | SCL             | P port         |     | 200 | ns   |

| t <sub>ps</sub> | Input data setup time      | P port          | SCL            | 150 |     | ns   |

| t <sub>ph</sub> | Input data hold time       | P port          | SCL            | 1   |     | μs   |

Product Folder Link(s): TCA9535

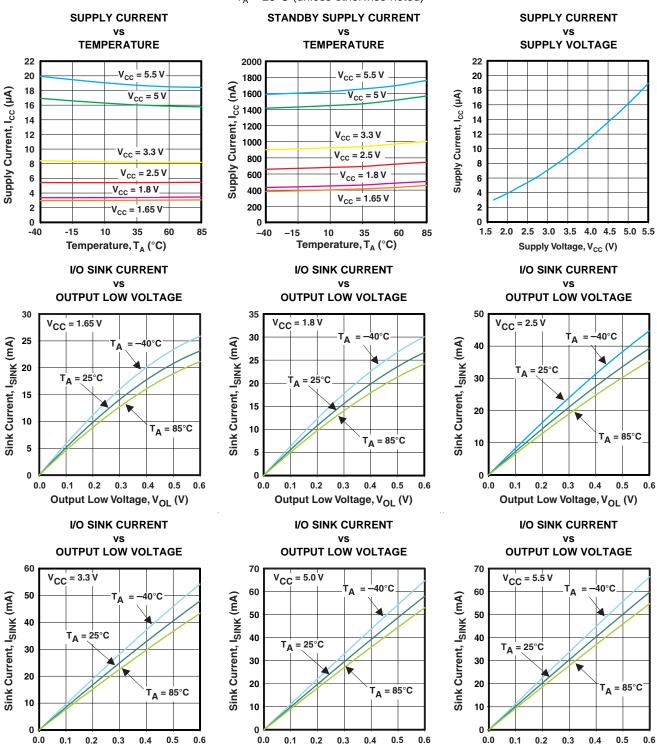

#### TYPICAL CHARACTERISTICS

$T_A = 25$ °C (unless otherwise noted)

Output Low Voltage, V<sub>OL</sub> (V)

Output Low Voltage, V<sub>OL</sub> (V)

Output Low Voltage, VOI (V)

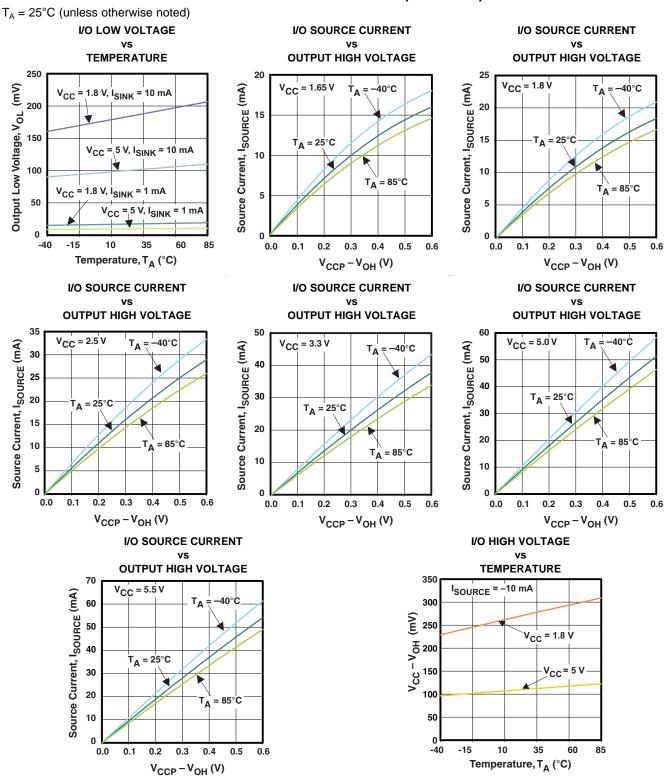

#### TYPICAL CHARACTERISTICS (continued)

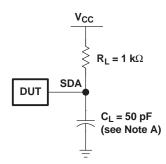

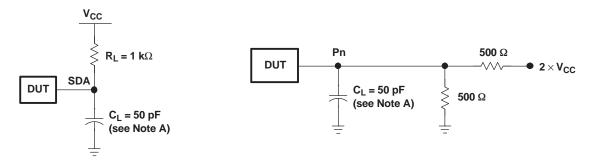

#### PARAMETER MEASUREMENT INFORMATION

#### **SDA LOAD CONFIGURATION**

#### **VOLTAGE WAVEFORMS**

| BYTE | DESCRIPTION              |  |  |  |

|------|--------------------------|--|--|--|

| 1    | I <sup>2</sup> C address |  |  |  |

| 2, 3 | P-port data              |  |  |  |

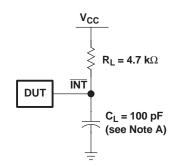

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50~\Omega$ ,  $t_r/t_f \leq$  30 ns.

- C. All parameters and waveforms are not applicable to all devices.

Figure 12. I<sup>2</sup>C Interface Load Circuit and Voltage Waveforms

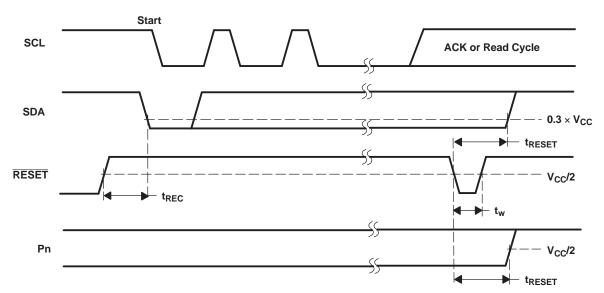

## PARAMETER MEASUREMENT INFORMATION (continued)

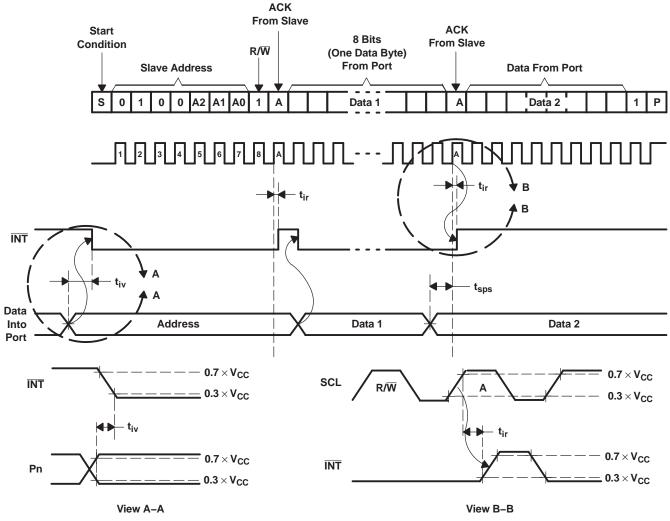

#### INTERRUPT LOAD CONFIGURATION

- A. C<sub>L</sub> includes probe and jig capacitance.

- All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50~\Omega$ ,  $t_r/t_f \leq$  30 ns.

- All parameters and waveforms are not applicable to all devices.

Figure 13. Interrupt Load Circuit and Voltage Waveforms

Copyright © 2009, Texas Instruments Incorporated Submit Documentation Feedback

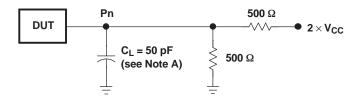

# PARAMETER MEASUREMENT INFORMATION (continued)

P-PORT LOAD CONFIGURATION

WRITE MODE  $(R/\overline{W} = 0)$

- A.  $C_L$  includes probe and jig capacitance.

- B.  $t_{pv}$  is measured from 0.7 ×  $V_{CC}$  on SCL to 50% I/O (Pn) output.

- C. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50 \Omega$ ,  $t_r/t_f \leq$  30 ns.

- D. The outputs are measured one at a time, with one transition per measurement.

- E. All parameters and waveforms are not applicable to all devices.

Figure 14. P-Port Load Circuit and Voltage Waveforms

# PARAMETER MEASUREMENT INFORMATION (continued)

**SDA LOAD CONFIGURATION**

P-PORT LOAD CONFIGURATION

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_r/t_f \leq$  30 ns.

- C. The outputs are measured one at a time, with one transition per measurement.

- D. I/Os are configured as inputs.

- E. All parameters and waveforms are not applicable to all devices.

Figure 15. Reset Load Circuits and Voltage Waveforms

Copyright © 2009, Texas Instruments Incorporated

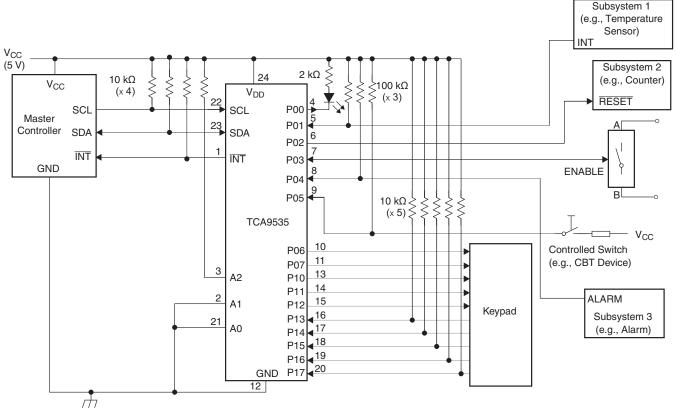

#### **APPLICATION INFORMATION**

Figure 16 shows an application in which the TCA9535 can be used.

- A. Device address is configured as 0100100 for this example.

- B. P00, P02, and P03 are configured as outputs.

- C. P01, P04–P07, and P10–P17 are configured as inputs.

- D. Pin numbers shown are for the PW package.

Figure 16. Typical Application

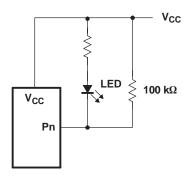

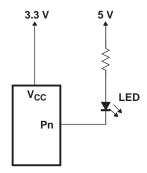

### Minimizing I<sub>CC</sub> When I/O Is Used to Control LED

When an I/O is used to control an LED, normally it is connected to  $V_{CC}$  through a resistor as shown in Figure 16. Because the LED acts as a diode, when the LED is off, the I/O  $V_{IN}$  is about 1.2 V less than  $V_{CC}$ . The  $\Delta I_{CC}$  parameter in Electrical Characteristics shows how  $I_{CC}$  increases as  $V_{IN}$  becomes lower than  $V_{CC}$ . For battery-powered applications, it is essential that the voltage of I/O pins is greater than or equal to  $V_{CC}$ , when the LED is off, to minimize current consumption.

Figure 17 shows a high-value resistor in parallel with the LED. Figure 18 shows  $V_{CC}$  less than the LED supply voltage by at least 1.2 V. Both of these methods maintain the I/O  $V_{IN}$  at or above  $V_{CC}$  and prevent additional supply-current consumption when the LED is off.

Figure 17. High-Value Resistor in Parallel With LED

Figure 18. Device Supplied by Lower Voltage

#### **Power-On Reset Requirements**

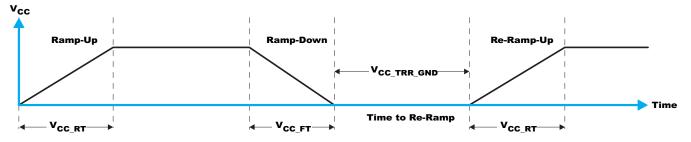

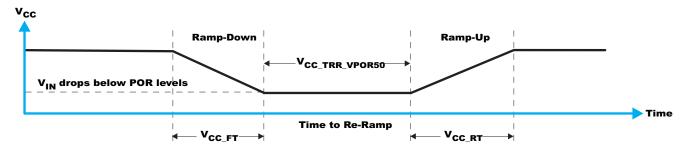

In the event of a glitch or data corruption, TCA9535 can be reset to its default conditions by using the power-on reset feature. Power-on reset requires that the device go through a power cycle to be completely reset. This reset also happens when the device is powered on for the first time in an application.

The two types of power-on reset are shown in Figure 19 and Figure 20.

Figure 19. V<sub>CC</sub> is Lowered Below 0.2 V or 0 V and Then Ramped Up to V<sub>CC</sub>

Copyright © 2009, Texas Instruments Incorporated

Figure 20. V<sub>CC</sub> is Lowered Below the POR Threshold, Then Ramped Back Up to V<sub>CC</sub>

Table 8 specifies the performance of the power-on reset feature for TCA9535 for both types of power-on reset.

Table 8. RECOMMENDED SUPPLY SEQUENCING AND RAMP RATES(1)

|                           | MIN                                                                                                            | TYP           | MAX | UNIT |      |    |

|---------------------------|----------------------------------------------------------------------------------------------------------------|---------------|-----|------|------|----|

| V <sub>CC_FT</sub>        | Fall rate                                                                                                      | See Figure 19 | 0.1 |      | 2000 | ms |

| V <sub>CC_RT</sub>        | Rise rate                                                                                                      | See Figure 19 | 0.1 |      | 2000 | ms |

| V <sub>CC_TRR_GND</sub>   | Time to re-ramp (when V <sub>CC</sub> drops to GND)                                                            | See Figure 19 | 1   |      |      | μs |

| V <sub>CC_TRR_POR50</sub> | Time to re-ramp (when V <sub>CC</sub> drops to V <sub>POR_MIN</sub> – 50 mV)                                   | See Figure 20 | 1   |      |      | μs |

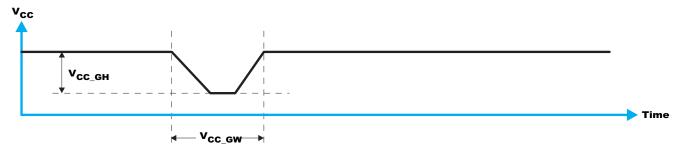

| V <sub>CC_GH</sub>        | Level that $V_{CCP}$ can glitch down to, but not cause a functional disruption when $V_{CCX\_GW}$ = 1 $\mu s$  | See Figure 21 |     |      | 1.2  | V  |

| V <sub>CC_GW</sub>        | Glitch width that will not cause a functional disruption when $V_{\text{CCX\_GH}} = 0.5 \times V_{\text{CCx}}$ | See Figure 21 |     |      | 10   | μs |

| $V_{PORF}$                | Voltage trip point of POR on falling V <sub>CC</sub>                                                           |               | 0.7 |      |      | V  |

| $V_{PORR}$                | Voltage trip point of POR on fising V <sub>CC</sub>                                                            |               |     |      | 1.4  | V  |

<sup>(1)</sup>  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  (unless otherwise noted)

Glitches in the power supply can also affect the power-on reset performance of this device. The glitch width  $(V_{CC\_GW})$  and height  $(V_{CC\_GH})$  are dependent on each other. The bypass capacitance, source impedance, and device impedance are factors that affect power-on reset performance. Figure 21 and Table 8 provide more information on how to measure these specifications.

Figure 21. Glitch Width and Glitch Height

$V_{POR}$  is critical to the power-on reset.  $V_{POR}$  is the voltage level at which the reset condition is released and all the registers and the I<sup>2</sup>C/SMBus state machine are initialized to their default states. The value of  $V_{POR}$  differs based on the  $V_{CC}$  being lowered to or from 0. Figure 22 and Table 8 provide more details on this specification.

Figure 22. V<sub>POR</sub>

# PACKAGE OPTION ADDENDUM

20-May-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | _       | Pins | U    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        |                  | (3)                 |              | (4/5)          |         |

| TCA9535PWR       | ACTIVE | TSSOP        | PW      | 24   | 2000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM  | -40 to 85    | PW535          | Samples |

| TCA9535RTWR      | ACTIVE | WQFN         | RTW     | 24   | 3000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PW535          | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 28-Aug-2012

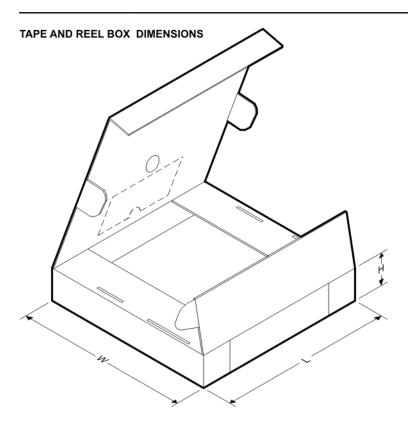

# TAPE AND REEL INFORMATION

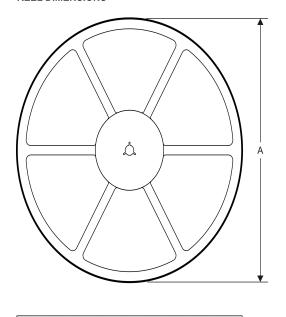

#### **REEL DIMENSIONS**

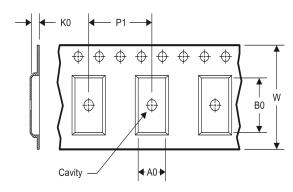

# TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### TAPE AND REEL INFORMATION

## \*All dimensions are nominal

| 7 til dilliononono aro momina |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-------------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TCA9535PWR                    | TSSOP           | PW                 | 24 | 2000 | 330.0                    | 16.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 16.0      | Q1               |

| TCA9535RTWR                   | WQFN            | RTW                | 24 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com 28-Aug-2012

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TCA9535PWR  | TSSOP        | PW              | 24   | 2000 | 367.0       | 367.0      | 38.0        |

| TCA9535RTWR | WQFN         | RTW             | 24   | 3000 | 367.0       | 367.0      | 35.0        |

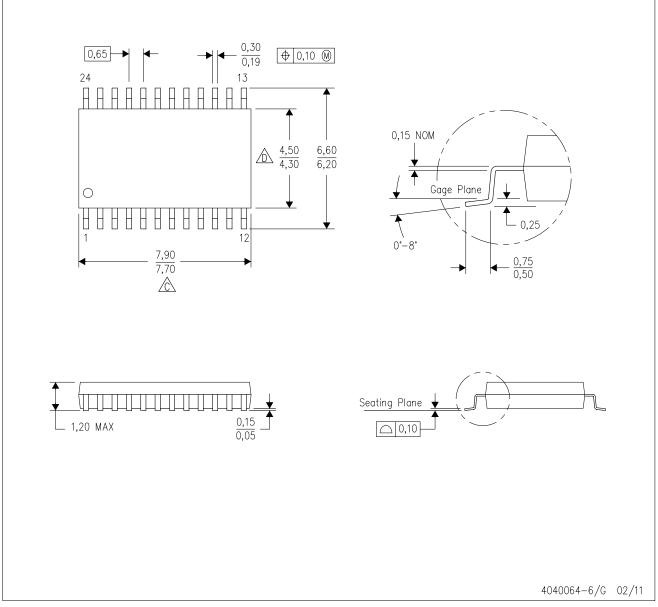

PW (R-PDSO-G24)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

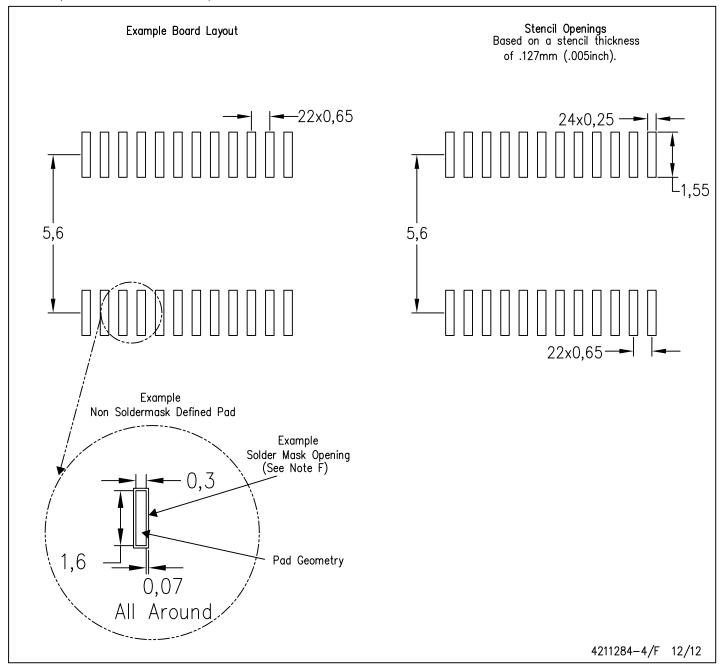

PW (R-PDSO-G24)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

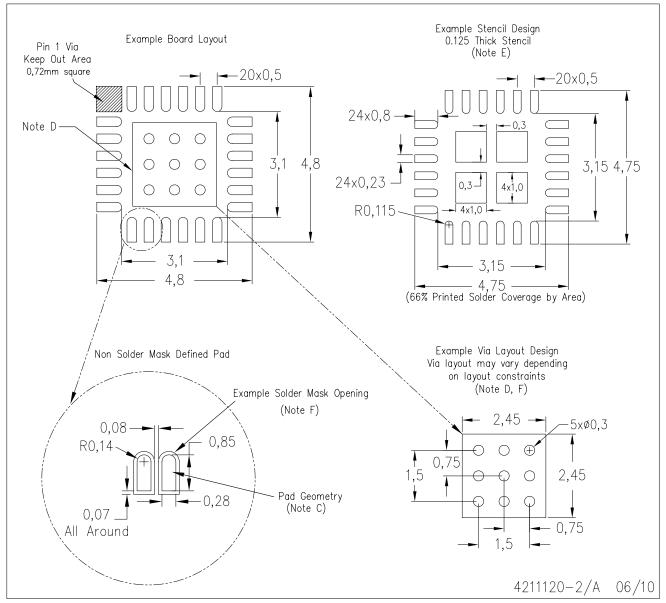

- C. Publication IPC-7351 is recommended for alternate design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

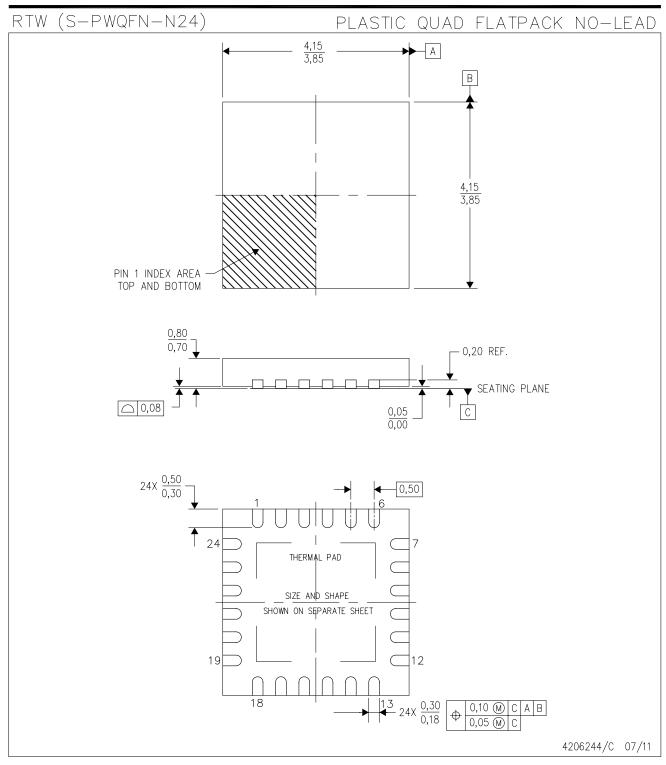

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-Leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

# RTW (S-PWQFN-N24)

# PLASTIC QUAD FLATPACK NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4206249-3/L 07/11

NOTES: A. All linear dimensions are in millimeters

# RTW (S-PWQFN-N24)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>