# **Cyclone IV GX Transceiver Starter Board**

# **Reference Manual**

101 Innovation Drive San Jose, CA 95134 www.altera.com Document Version: Document Date:

1.0 March 2010

Copyright © 2010 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter 1. Overview                           |        |

|-----------------------------------------------|--------|

| Introduction                                  |        |

| General Description                           |        |

| Board Component Blocks                        |        |

| Starter Board Block Diagram                   | 1–4    |

| Handling the Board                            | 1–4    |

| Chapter 2. Board Components                   |        |

| Introduction                                  | 2–1    |

| Board Overview                                | 2–1    |

| Featured Device: Cyclone IV GX Device         |        |

| I/O Resources                                 |        |

| MAX II CPLD EPM2210 System Controller         |        |

| Configuration, Status, and Setup Elements     |        |

| Configuration                                 |        |

| FPGA Configuration over Embedded USB-Blaster  |        |

| FPGA Configuration from Flash Memory          |        |

| FPGA Configuration using External USB-Blaster |        |

| FPGA Configuration using EPCS Device          |        |

| Status Elements                               |        |

| Setup Elements                                |        |

| Board Settings DIP Switch                     |        |

| Configuration Settings DIP Switch             |        |

| Configuration Push-Button Switches            |        |

| Clock Circuitry                               |        |

| Cyclone IV GX Transceiver Clock Inputs        |        |

| General User Input/Output                     |        |

| User-Defined Push-Button Switches             | 2–17   |

| User-Defined LEDs                             | 2–17   |

| LCD                                           | 2–18   |

| Components and Transceiver Interfaces         | 2–19   |

| PCI Express                                   | 2–19   |

| 10/100/1000 Ethernet                          |        |

| Transceiver SMA Connectors (Optional)         | 2–22   |

| Memory                                        | 2–22   |

| SSRAM                                         | 2–22   |

| Flash                                         | 2–24   |

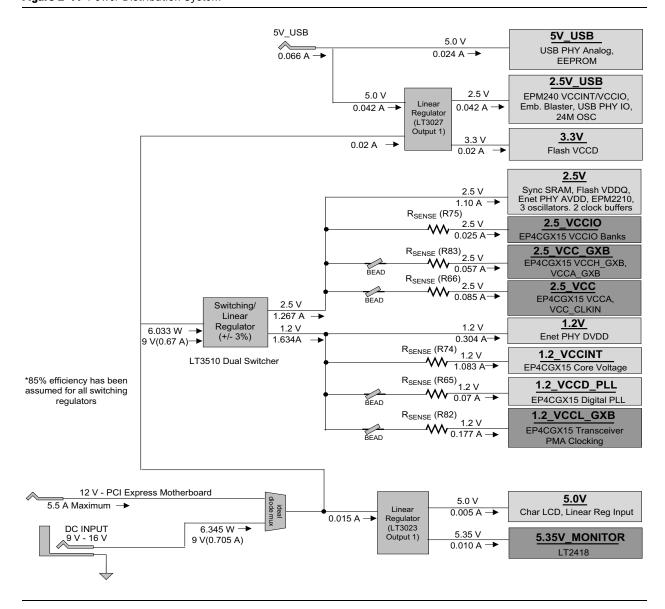

| Power Supply                                  | 2–26   |

| Power Distribution System                     |        |

| Power Measurement                             | 2–28   |

| Statement of China-RoHS Compliance            | 2–29   |

| Additional Information                        |        |

| Revision History                              | Info-1 |

| How to Contact Altera                         |        |

| Typographic Conventions                       |        |

|                                               |        |

### Introduction

This document describes the hardware features of the Cyclone® IV GX Transceiver starter board, including the detailed pin-out and component reference information required to create custom FPGA designs that interface with all components of the board.

# **General Description**

The Cyclone IV GX transceiver starter board provides a hardware platform for developing and prototyping low-power, high-volume, feature-rich designs as well as to demonstrate the Cyclone IV GX device's on-chip memory, embedded multipliers, and the Nios® II embedded soft processor. The board provides peripherals and memory interfaces to facilitate the development of the Cyclone IV GX transceiver designs.

The Cyclone IV GX transceiver starter board is especially suitable for cost-sensitive applications that require high-speed transceivers and power integrity solutions.

For more information on the Cyclone IV device family, refer to the *Cyclone IV Device Handbook*.

# **Board Component Blocks**

The board features the following major component blocks:

- Cyclone IV GX EP4CGX15BF14 FPGA in the 169-pin FineLine BGA (FBGA) package

- 14,400 LEs

- 540-kilobit (Kb) on-die memory

- 20 global clocks

- 72 user I/Os

- 3 phase locked loops (PLLs)

- 1 PCI Express hard IP block

- 1.2-V core power

- MAX® II EPM2210F256 CPLD in the 256-pin FBGA package

- 2.5-V core power

- MAX II EPM240M100 CPLD in the 100-pin Micro FBGA (MBGA) package

- FPGA configuration circuitry

- MAX II CPLD EPM2210 System Controller and flash passive serial (PS) configuration

- On-board USB-Blaster<sup>TM</sup> for use with the Quartus<sup>®</sup> II Programmer

- JTAG header for external USB-Blaster with the Quartus II Programmer

- Erasable programmable configurable serial (EPCS) device

- On-Board ports

- USB 2.0

- One gigabit Ethernet port

- Transceiver interfaces

- PCI Express x1 edge connector

- 10/100/1000BASE-T Ethernet PHY with RJ-45 connector

- One optional TX/RX transceiver to SMA connectors (requires a minor modification on the board)

- On-Board memory

- 18-megabit (Mb) Synchronous Static Random Access Memory (SSRAM)

- 128-Mb flash

- On-Board clocking circuitry

- 6-MHz, 24-MHz, 25-MHz, and 50-MHz oscillators

- 125-MHz LVDS oscillator

- SMA clock input

- General user I/O

- LEDs and display

- Four FPGA user LEDs

- One configuration done LED

- One max error LED

- Five Ethernet status LEDs

- One USB status LED

- One power status LED

- Two PGM LEDs

- A two-line character LCD display

- Push-Button switches

- One CPU reset push-button switch

- One MAX II configuration reset push-button switch

- One PGM configure push-button switch (configure the FPGA from flash memory)

- One PGM select push-button switch (select image to load from flash memory)

- Two general user push-button switches

- DIP switches

- Board setting DIP switch

- Configuration setting DIP switch

- Power supply

- 9-V 16-V DC input

- 2.5-mm barrel jack for DC power input

- On/Off slide power switch

- On-Board power measurement circuitry

- Mechanical

- 6.6" x 2.713" board

- PCI Express chassis or bench-top operation

# **Starter Board Block Diagram**

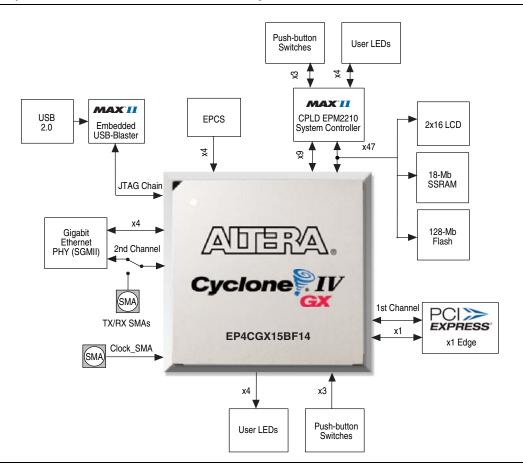

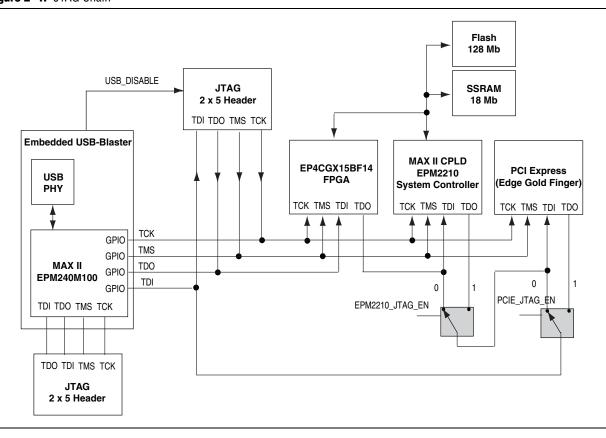

Figure 1–1 shows the block diagram of the Cyclone IV GX transceiver starter board.

Figure 1–1. Cyclone IV GX transceiver Starter Board Block Diagram

# **Handling the Board**

When handling the board, it is important to observe the following static discharge precaution:

Without proper anti-static handling, the board can be damaged. Therefore, use anti-static handling precautions when touching the board.

# 2. Board Components

### Introduction

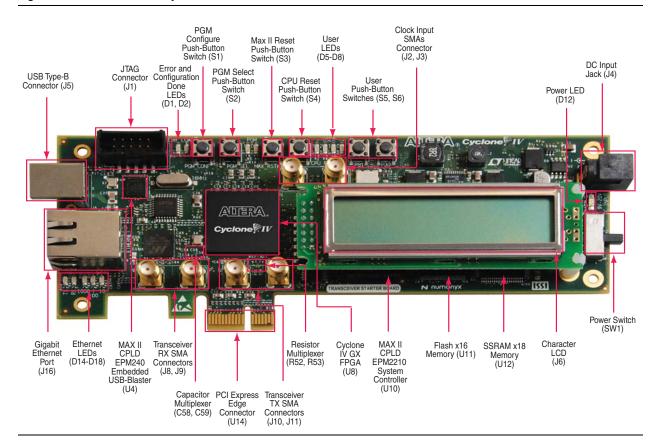

This chapter introduces the major components on the Cyclone IV GX Transceiver starter board. Figure 2–1 illustrates major component locations and Table 2–1 provides a brief description of all component features of the board.

A complete set of schematics, a physical layout database, and GERBER files for the starter board reside in the Cyclone IV GX Transceiver starter kit documents directory.

For information about powering up the board and installing the demonstration software, refer to the *Cyclone IV GX Transceiver Starter Kit User Guide*.

This chapter consists of the following sections:

- "Board Overview"

- "Featured Device: Cyclone IV GX Device" on page 2–4

- "MAX II CPLD EPM2210 System Controller" on page 2–6

- "Configuration, Status, and Setup Elements" on page 2–9

- "Clock Circuitry" on page 2–16

- "General User Input/Output" on page 2–17

- "Components and Transceiver Interfaces" on page 2–19

- "Memory" on page 2–22

- "Power Supply" on page 2–26

- "Statement of China-RoHS Compliance" on page 2–29

### **Board Overview**

This section provides an overview of the Cyclone IV GX Transceiver starter board, including an annotated board image and component descriptions. Figure 2–1 provides an overview of the starter board features.

Figure 2–1. Overview of the Cyclone IV GX Transceiver Starter Board Features

Table 2–1 describes the components and lists their corresponding board references.

**Table 2–1.** Cyclone IV GX Transceiver Starter Board Components (Part 1 of 3)

| Board Reference    | Type Description                    |                                                                                                                                                                                                                       |  |

|--------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Featured Devices   |                                     |                                                                                                                                                                                                                       |  |

| U8                 | FPGA                                | EP4CGX15BF14, 169-pin FBGA.                                                                                                                                                                                           |  |

| U10                | CPLD                                | EPM2210F256, 256-pin FBGA.                                                                                                                                                                                            |  |

| Configuration, Sta | itus, and Setup Elements            |                                                                                                                                                                                                                       |  |

| J5                 | USB Type-B connector                | Connects to the computer to enable embedded USB-Blaster JTAG.                                                                                                                                                         |  |

| J13                | JTAG chain header                   | Enables and disables devices in the JTAG chain.                                                                                                                                                                       |  |

| S8                 | Board settings DIP switch           | Controls the MAX II CPLD EPM2210 System Controller functions such as clock select, SMA clock input control, and which image to load from flash memory at power-up. This switch is located at the bottom of the board. |  |

| J1                 | JTAG connector                      | Disables embedded blaster (for use with external USB-Blasters).                                                                                                                                                       |  |

| U15                | EPCS128 serial configuration device | Flash memory device with a serial interface which stores configuration data for FPGA device that supports active serial configuration and reloads the data to the FPGA upon power-up or reconfiguration.              |  |

Table 2–1. Cyclone IV GX Transceiver Starter Board Components (Part 2 of 3)

| <b>Board Reference</b>     | Туре                              | Description                                                                                                                                                  |  |  |

|----------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D2                         | Load LED                          | Illuminates when the MAX II CPLD EPM2210 System Controller is actively configuring the FPGA.                                                                 |  |  |

| D1                         | Error LED                         | Illuminates when the FPGA configuration from flash memory fails.                                                                                             |  |  |

| D14, D15, D16,<br>D17, D18 | Ethernet LEDs                     | Shows the connection speed as well as transmit or receive activity.                                                                                          |  |  |

| D12                        | Power LED                         | Illuminates when 9-V – 16-V DC power is present.                                                                                                             |  |  |

| S7                         | Configuration settings DIP switch | Sets the configuration mode to either passive serial (flash) or active serial (EPCS). This switch is located at the bottom of the board.                     |  |  |

| S4                         | CPU reset push-button switch      | Press to reset the FPGA logic.                                                                                                                               |  |  |

| S3                         | MAX II reset push-button switch   | Press to reset the MAX II CPLD EPM2210 System Controller.                                                                                                    |  |  |

| S2                         | PGM select push-button switch     | Toggles the PGM LEDs which selects the program image that loads from flash memory to the FPGA.                                                               |  |  |

| S1                         | PGM configure push-button switch  | Configure the FGPA from flash memory based on the PGM LEDs setting.                                                                                          |  |  |

| <b>Clock Circuitry</b>     |                                   |                                                                                                                                                              |  |  |

| X1                         | 125-MHz oscillator                | 125-MHz crystal oscillator for PCI Express or general use such as memories. Multiplexed with CLKIN_SMA_P/N signals based on CLK_SEL switch value.            |  |  |

| X5                         | 50-MHz oscillator                 | 50-MHz crystal oscillator for configuration purpose. This oscillator is located at the bottom of the board.                                                  |  |  |

| J2, J3                     | Clock input SMAs                  | Drive LVPECL-compatible clock inputs into the clock multiplexer buffer (U6).                                                                                 |  |  |

| General User Inpu          | t/Output                          |                                                                                                                                                              |  |  |

| D5, D6, D7, D8             | User LEDs                         | Four user LEDs. Illuminates when driven low.                                                                                                                 |  |  |

| S5, S6                     | User push-button switches         | Two user push-button switches. Driven low when pressed.                                                                                                      |  |  |

| J6                         | Character LCD                     | Connector which interfaces to the provided 16 character × 2 line LCD module.                                                                                 |  |  |

| Memory Devices             |                                   |                                                                                                                                                              |  |  |

| U12                        | SSRAM x18 memory                  | Standard synchronous RAM which provides a 2-MB SSRAM port.                                                                                                   |  |  |

| U11                        | Flash x16 memory                  | Synchronous burst mode flash device which provides a 16-MB non-volatile memory port.                                                                         |  |  |

| Components and 1           | ransceiver Interfaces             |                                                                                                                                                              |  |  |

| J7                         | RJ-45 connector                   | Provides 10/100/1000 BASE-T Ethernet connection via a Marvell 88E1111 PHY and the FPGA-based Altera Triple Speed Ethernet MegaCore function in SGMII mode.   |  |  |

| U9                         | Gigabit Ethernet                  | A Marvell 88E1111 PHY device for 10/100/1000 BASE-T Ethernet connection. The device is an auto-negotiating Ethernet PHY with ar SGMII interface to the FPGA. |  |  |

| U14                        | PCI Express edge connector        | Interfaces to a PCI Express root port such as an appropriate PC motherboard. Made of gold-plated edge fingers for up to ×1 signaling in Gen1 mode.           |  |  |

| Board Reference           | Type                     |                                    |  |

|---------------------------|--------------------------|------------------------------------|--|

| <b>Table 2–1.</b> Cyclone | IV GX Transceiver Starte | ter Board Components (Part 3 of 3) |  |

| Board Reference       | Туре                                 | Description                                                                                                                                                                     |

|-----------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J8, J9                | Transceiver RX SMA connectors        | Two input SMAs (optional) to the high-speed positive and negative differential receiver channel. These connectors cannot be used together with the Gigabit Ethernet port.       |

| J10, J11              | Transceiver TX SMA connectors        | Two output SMAs (optional) from the high-speed positive and negative differential transmitter channel. These connectors cannot be used together with the Gigabit Ethernet port. |

| C57, C58, C59,<br>C60 | Transceiver RX capacitor multiplexer | Capacitor multiplexer which requires a minor modification on the board if the optional transceiver RX SMA connectors (J8, J9) are used.                                         |

| R51, R52, R53,<br>R54 | Transceiver TX resistor multiplexer  | Resistor multiplexer which requires a minor modification on the board if the optional transceiver TX SMA connectors (J11, J10) are used.                                        |

| Power Supply          |                                      |                                                                                                                                                                                 |

| J4                    | DC input jack                        | Accepts a 9-V – 16-V DC power supply. Do not use this input jack while the board is plugged into a PCI Express slot.                                                            |

| SW1                   | Power switch                         | Switch to power on or off the board when power is supplied from the DC input jack.                                                                                              |

# **Featured Device: Cyclone IV GX Device**

The Cyclone IV GX Transceiver starter board features the Cyclone IV GX EP4CGX15BF14 device (U8) in a 169-pin FBGA package.

For more information about Cyclone IV device family, refer to the Cyclone IV Device Handbook.

Table 2–2 describes the features of the Cyclone IV GX EP4CGX15BF14 device.

**Table 2–2.** Cyclone IV GX EP4CGX15BF14 Device Features

| Equivalent LEs | M9K RAM Blocks<br>(Kbits) | Embedded<br>Memory (Kbits) | 18-bit × 18-bit<br>Multipliers | Transceivers<br>(2.5 Gbps) | PLLs | Package Type |

|----------------|---------------------------|----------------------------|--------------------------------|----------------------------|------|--------------|

| 14,400         | 9                         | 540                        | 0                              | 2                          | 3    | 169-pin FBGA |

Table 2–3 lists the Cyclone IV GX device component reference and manufacturing information.

**Table 2–3.** Cyclone IV GX Device Component Reference and Manufacturing Information

| Board Reference | Description                                                         | Manufacturer       | Manufacturing<br>Part Number | Manufacturer<br>Website |

|-----------------|---------------------------------------------------------------------|--------------------|------------------------------|-------------------------|

| U8              | FPGA, Cyclone IV GX,<br>169-pin FBGA package, 14K<br>LEs, lead-free | Altera Corporation | EP4CGX15BF14                 | www.altera.com          |

### I/O Resources

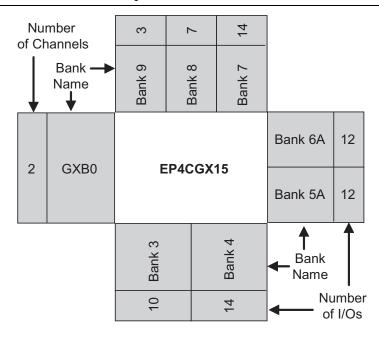

Figure 2–2 illustrates the bank organization and I/O count for the EP4CGX15BF14 device in the 169-pin FBGA package.

Figure 2-2. EP4CGX15BF14 Device I/O Bank Diagram

Table 2–4 lists the Cyclone IV GX device pin count and usage by function on the starter board.

**Table 2–4.** Cyclone IV GX Device I/O Pin Count and Usage (Note 1)

| Function                                       | I/O Standard      | I/O Count        | Special Pins                                   |

|------------------------------------------------|-------------------|------------------|------------------------------------------------|

| Flash, SSRAM, FSML Bus                         |                   | 47               | 1 DEV_OE                                       |

| Gigabit Ethernet                               |                   | 4                | _                                              |

| Buttons                                        | 2.5-V CMOS        | 3                | 1 DEV_CLRn                                     |

| LCD                                            |                   | 1                | _                                              |

| LEDs                                           |                   | 4                | 1 INIT_DONE, 1 nCEO                            |

| Clocks or Oscillators                          | 2.5-V CMOS + LVDS | 7                | 3 differential clock input pair, 1 clock input |

| PCI Express                                    |                   | 1                | _                                              |

| Passive serial and active serial configuration | 2.5-V CMOS        | 4                | _                                              |

| Device I/O Total:                              |                   | <b>71/72</b> (2) |                                                |

#### Notes to Table 2-4:

- (1) 60 out of 72 user I/Os are bidirectional I/O pins while the other 12 pins are for clock inputs only.

- (2) The total I/O count excludes the transceiver bank.

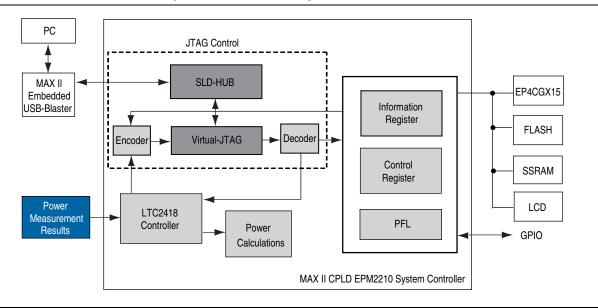

# **MAX II CPLD EPM2210 System Controller**

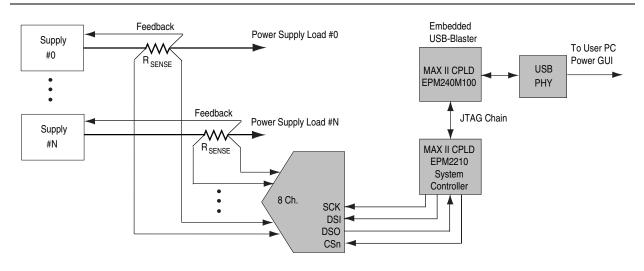

The board utilizes the EPM2210 System Controller, an Altera MAXII CPLD, for the following purposes:

- FPGA configuration from flash memory

- Power consumption monitoring

- Virtual JTAG interface for PC-based GUI

- Control registers for clocks

- Control registers for remote system update

Figure 2–3 illustrates the MAX II CPLD EPM2210 System Controller's functionality and external circuit connections as a block diagram.

Figure 2-3. MAX II CPLD EPM2210 System Controller Block Diagram

Table 2–5 lists the I/O signals present on the MAX II CPLD EPM2210 System Controller. The signal names and functions are relative to the MAX II device (U10).

Table 2-5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 1 of 3)

| Schematic Signal Name | I/O<br>Standard | EPM2210<br>Pin Number | EP4CGX15BF14<br>Pin Number | Description                          |

|-----------------------|-----------------|-----------------------|----------------------------|--------------------------------------|

| CLK125_EN             |                 | R1                    | _                          | 125-MHz oscillator enable            |

| CLK125_SDA            | 1               | T2                    | _                          | 125-MHz programming data             |

| CLK125_SCK            |                 | R3                    | _                          | 125-MHz programming clock            |

| CLK_SEL               | 2.5-V           | R4                    | <del></del>                | DIP - clock select SMA or oscillator |

| CLK_MAXII             | 2.0-V           | J5                    | _                          | MAX II clock input                   |

| EPCS_nCS              |                 | B13                   | C5                         | EPCS memory chip enable              |

| FLASH_CEn             |                 | A2                    | B8                         | FSML bus flash memory chip enable    |

| FSML_OEn              |                 | B1                    | B13                        | FSML bus flash memory output enable  |

Table 2–5.

MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 2 of 3)

| Schematic Signal Name | I/O<br>Standard | EPM2210<br>Pin Number | EP4CGX15BF14<br>Pin Number | Description                          |

|-----------------------|-----------------|-----------------------|----------------------------|--------------------------------------|

| FSML_WEn              |                 | C5                    | A13                        | FSML bus flash memory write enable   |

| FPGA_CONF_DONE        |                 | M2                    | J5                         | FPGA configuration done              |

| FPGA_CONFIG_D0        |                 | N2                    | A5                         | FPGA configuration data              |

| FPGA_nCONFIG          |                 | M1                    | D5                         | FPGA configuration active            |

| FPGA_nSTATUS          |                 | L2                    | K6                         | FPGA configuration ready             |

| FPGA_DCLK             |                 | L1                    | A4                         | FPGA configuration clock             |

| JTAG_TCK              |                 | P3                    | В3                         | FPGA JTAG TCK                        |

| JTAG_TMS              |                 | N4                    | A2                         | FPGA JTAG TMS                        |

| JTAG_FPGA_TDO         |                 | L6                    | A1                         | FPGA JTAG TDO                        |

| JTAG_EPM2210_TDO      |                 | M5                    | _                          | MAX II JTAG TDO                      |

| FPGA_MSEL0            |                 | B16                   | K5                         | FPGA MSEL0 configuration mode select |

| FPGA_MSEL1            |                 | A15                   | N3                         | FPGA MSEL1 configuration mode select |

| FPGA_MSEL2            |                 | B14                   | L3                         | FPGA MSEL2 configuration mode select |

| FSML_A1               |                 | P15                   | A6                         | FSML bus address                     |

| FSML_A2               |                 | N15                   | B6                         | FSML bus address                     |

| FSML_A3               |                 | N16                   | C6                         | FSML bus address                     |

| FSML_A4               |                 | M15                   | A8                         | FSML bus address                     |

| FSML_A5               |                 | M16                   | A7                         | FSML bus address                     |

| FSML_A6               |                 | L15                   | M11                        | FSML bus address                     |

| FSML_A7               | 2.5-V           | L16                   | N12                        | FSML bus address                     |

| FSML_A8               |                 | K15                   | K10                        | FSML bus address                     |

| FSML_A9               |                 | K16                   | L11                        | FSML bus address                     |

| FSML_A10              |                 | J15                   | M9                         | FSML bus address                     |

| FSML_A11              |                 | J16                   | N10                        | FSML bus address                     |

| FSML_A12              |                 | H16                   | N11                        | FSML bus address                     |

| FSML_A13              |                 | H15                   | H10                        | FSML bus address                     |

| FSML_A14              |                 | G16                   | H12                        | FSML bus address                     |

| FSML_A15              |                 | G15                   | N13                        | FSML bus address                     |

| FSML_A16              |                 | F16                   | M13                        | FSML bus address                     |

| FSML_A17              |                 | F15                   | J13                        | FSML bus address                     |

| FSML_A18              |                 | E16                   | K13                        | FSML bus address                     |

| FSML_A19              |                 | E15                   | L12                        | FSML bus address                     |

| FSML_A20              |                 | D16                   | L13                        | FSML bus address                     |

| FSML_A21              |                 | D15                   | K11                        | FSML bus address                     |

| FSML_A22              |                 | C15                   | K12                        | FSML bus address                     |

| FSML_A23              |                 | C14                   | D13                        | FSML bus address                     |

| FSML_D0               | ]               | A9                    | D11                        | FSML bus data                        |

| FSML_D1               |                 | A8                    | D12                        | FSML bus data                        |

| FSML_D2               | ]               | B8                    | E10                        | FSML bus data                        |

Table 2–5.

MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 3)

| Schematic Signal Name | I/O<br>Standard | EPM2210<br>Pin Number | EP4CGX15BF14<br>Pin Number | Description                                           |

|-----------------------|-----------------|-----------------------|----------------------------|-------------------------------------------------------|

| FSML_D3               |                 | A7                    | F9                         | FSML bus data                                         |

| FSML_D4               |                 | B7                    | E13                        | FSML bus data                                         |

| FSML_D5               |                 | C8                    | F10                        | FSML bus data                                         |

| FSML_D6               |                 | A6                    | F11                        | FSML bus data                                         |

| FSML_D7               |                 | B6                    | G9                         | FSML bus data                                         |

| FSML_D8               |                 | A5                    | G10                        | FSML bus data                                         |

| FSML_D9               |                 | B5                    | A12                        | FSML bus data                                         |

| FSML_D10              |                 | C7                    | A11                        | FSML bus data                                         |

| FSML_D11              |                 | A4                    | B11                        | FSML bus data                                         |

| FSML_D12              |                 | B4                    | B10                        | FSML bus data                                         |

| FSML_D13              |                 | C4                    | C11                        | FSML bus data                                         |

| FSML_D14              |                 | C6                    | C12                        | FSML bus data                                         |

| FSML_D15              |                 | В3                    | C8                         | FSML bus data                                         |

| CONF_DONE_LED         |                 | T11                   | _                          | FPGA configuration done LED                           |

| MAX_ERROR             |                 | Т8                    | _                          | FPGA configuration error LED                          |

| MAX_RESETn            |                 | M9                    | _                          | MAX II reset push-button switch                       |

| MAX_CSn               |                 | T12                   | L5                         | MAX II chip select                                    |

| PGM_CONFIG            | 2.5-V           | R10                   | _                          | Loads flash memory image identified by the PGM LEDs   |

| PGM_LED0              |                 | Т9                    | _                          | Flash memory PGM select indicator 0                   |

| PGM_LED1              |                 | R9                    | _                          | Flash memory PGM select indicator 1                   |

| PGM_SEL               |                 | T10                   | _                          | Toggles the PGM_LED[0:1] sequence                     |

| SENSE_CSn             |                 | J3                    | _                          | Power monitor chip select                             |

| SENSE_SCK             |                 | J1                    | _                          | Power monitor serial peripheral interface (SPI) clock |

| SENSE_SDI             |                 | J2                    | <del></del>                | Power monitor SPI data in                             |

| SENSE_SDO             |                 | K1                    | _                          | Power monitor SPI data out                            |

| SRAM_BWan             |                 | C2                    | L4                         | FSML bus SSRAM byte write enable                      |

| SRAM_BWbn             |                 | D2                    | M4                         | FSML bus SSRAM byte write enable                      |

| SRAM_CEn              |                 | E2                    | N6                         | FSML bus SSRAM chip enable                            |

| SRAM_ADSCn            |                 | F2                    | _                          | FSML bus SSRAM address status controller              |

| SRAM_ADSPn            |                 | F1                    | _                          | FSML bus SSRAM address status processor               |

| SRAM_ADVn             |                 | G2                    | _                          | FSML bus SSRAM address valid                          |

| SRAM_CLK              |                 | G1                    | L7                         | FSML bus SSRAM clock                                  |

Table 2–6 lists the MAX II CPLD EPM2210 System Controller component reference and manufacturing information.

**Table 2–6.** MAX II CPLD EPM2210 System Controller Component Reference and Manufacturing Information

| Board Reference | Description                                            | Description Manufacturer M |                | Manufacturer<br>Website |

|-----------------|--------------------------------------------------------|----------------------------|----------------|-------------------------|

| U10             | IC - MAX II CPLD EPM2210<br>256FBGA -3 LF 2.5 V VCCINT | Altera Corporation         | EPM2210F256C3N | www.altera.com          |

# **Configuration, Status, and Setup Elements**

This section describes the board's configuration, status, and setup elements.

### **Configuration**

This section describes the FPGA, flash memory, and MAX II CPLD EPM2210 System Controller device configuration methods supported by the Cyclone IV GX Transceiver starter board. The Cyclone IV GX Transceiver starter board supports the following configuration methods:

- Embedded USB-Blaster is the default method for configuring the FPGA at any time using the Quartus II Programmer in JTAG mode with the supplied USB cable.

- Flash memory download is used for storing FPGA images which the MAXII CPLD EPM2210 System Controller uses to configure the Cyclone IV GX device either on board power-up or after the PGM configure push-button switch (S8) is pressed.

- External USB-Blaster for configuring the FPGA using an external USB-Blaster.

- Serial configuration (EPCS) device (U15) is used to store configuration data for FPGA device that supports active serial (AS) configuration and reloads the data to the FPGA upon power-up or reconfiguration.

### **FPGA Configuration over Embedded USB-Blaster**

The USB-Blaster is implemented using a USB Type-B connector (J5), a FTDI USB 2.0 PHY device (U5), and an Altera MAX II CPLD (U4). This allows the configuration of the FPGA using a USB cable directly connected between the USB port on the board (J5) and a USB port of a PC running the Quartus II software. The JTAG chain is normally mastered by the embedded USB-Blaster found in the MAX II CPLD EPM240M100.

The embedded USB-Blaster is automatically disabled when an external USB-Blaster is connected to the JTAG chain. Figure 2–4 illustrates the JTAG chain.

The Cyclone IV GX FPGA is configured via JTAG using the MAX II configuration controller design (embedded blaster) as the primary configuration mode. The board includes a MAX II CPLD EPM2210 System Controller which interfaces directly to the Cyclone IV GX FPGA for configuration, LCD control, power monitor control, and other purposes. The MAX II CPLD EPM2210 System Controller contains the required state machine and control logic to determine the configuration source for the Cyclone IV GX FPGA.

Table 2–7 lists the Cyclone IV GX configuration modes.

Table 2-7. Cyclone IV GX Configuration Modes

|                     |          | Device |      |      |  |  |

|---------------------|----------|--------|------|------|--|--|

| Configuration Mode  | Flash    | MAX II | EPCS | JTAG |  |  |

| Passive Serial (PS) | <b>✓</b> | ✓      |      |      |  |  |

| Active Serial (AS)  |          |        | ✓    |      |  |  |

| Flash Source        | Numonyx  |        |      |      |  |  |

| JTAG                |          | ✓      |      | ✓    |  |  |

### **Flash Memory Programming**

Flash memory programming is possible through a variety of methods using the Cyclone IV GX device.

The default method is to use the factory design called the Board Update Portal. This design is an embedded webserver, which serves the Board Update Portal web page. The web page allows you to select new FPGA designs including hardware, software, or both in an industry-standard S-Record File (.flash) and write the design to the user hardware page (page 1) of the flash memory over the network.

The secondary method is to use the pre-built parallel flash loader (PFL) design included in the starter kit. The starter board implements the Altera PFL megafunction for flash memory programming. The PFL megafunction is a block of logic that is programmed into an Altera programmable logic device (FPGA or CPLD). The PFL functions as a utility for writing to a compatible flash memory device. This pre-built design contains the PFL megafunction that allows you to write either page 0, page 1, or other areas of flash memory over the USB interface using the Quartus II software. This method is used to restore the starter board to its factory default settings.

Other methods to program the flash memory can be used as well, including the Nios® II processor.

For more information on the Nios II processor, refer to the Nios II Processor page of the Altera website.

### **FPGA Configuration from Flash Memory**

On either power-up or by pressing the PGM configure push-button switch (S1), the MAX II CPLD EPM2210 System Controller's PFL configures the FPGA from the flash memory hardware page 0 or 1 based on whether PGM\_LED0 or PGM\_LED1 is illuminated. Table 2–8 defines the hardware page that loads when the PGM configure push-button switch (S1) is pressed. The PFL megafunction reads 16-bit data from the flash memory and converts the data to PS format. This 1-bit data is then written to the FPGA's dedicated configuration pins during configuration.

There are two pages reserved for the FPGA configuration data. The factory hardware page is considered page 0 and is loaded upon power-up if the USER\_PGM DIP switch (S8) is set to '0'. Otherwise, the user hardware page 1 is loaded. Pressing the PGM configure push-button switch (S1) loads the FPGA with a hardware page based on which PGM\_LED [1:0] (D3, D4) LED is illuminated. Table 2–8 defines the hardware page that loads when the PGM configure push-button switch (S1) is pressed.

| <b>Table 2–8.</b> PGM Configure Push-Button Switch (S1) LED Settings (No. | iote | " |

|---------------------------------------------------------------------------|------|---|

|---------------------------------------------------------------------------|------|---|

| PGM_LED0 | PGM_LED1            | Design           |

|----------|---------------------|------------------|

| ON       | ON                  | Factory hardware |

| ON       | OFF User hardware 1 |                  |

| OFF      | ON                  | User hardware 2  |

Note to Table 2-8:

(1) ON indicates that the LED is illuminated while OFF indicates that the LED is not illuminated.

### **FPGA Configuration using External USB-Blaster**

The JTAG programming header provides another method for configuring the FPGA using an external USB-Blaster device with the Quartus II Programmer running on a PC. The external USB-Blaster is connected to the board through the JTAG connector (J1). Figure 2–4 on page 2–10 illustrates the JTAG chain.

By default, the FPGA is the first device in the JTAG chain. To add the MAX II CPLD EPM2210 System Controller into the JTAG chain, set the board settings DIP switch (S8.3) to '0'. When the starter board is plugged into a PCI Express slot, you can add the PCI Express card into the JTAG chain by setting the board settings DIP switch (S8.4) to '1'. Table 2–11 on page 2–14 summarizes the board settings DIP switch controls.

### **FPGA Configuration using EPCS Device**

Active serial configuration can be performed using an Altera® EPCS device. During configuration, the FPGA is the master and the EPCS128 device is the slave. The configuration data is transferred to the FPGA on the DATA0 pin at a rate of one bit per clock cycle. This configuration data is synchronized to the DCLK input.

Before you program the EPCS device, set the configuration DIP switch (S7) to select the AS configuration scheme as shown in Table 2–13 on page 2–14. After programming the EPCS device, the design is loaded from the EPCS device to the FPGA when you power up the board.

### **EPCS Programming**

EPCS programming is possible through a variety of methods. One method to program the EPCS device is to use the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the FPGA that uses the JTAG connector (J1) to access the JTAG Indirect Configuration Device Programming File (.jic) and then uses the AS interface to program the EPCS device. Both the JTAG and AS interfaces are bridged together inside the SFL design.

Another method to program the EPCS device is to perform in-system programming through the AS programming header (J12).

Other methods to program the EPCS can be used as well, including the Nios II processor.

For more information on the following topics, refer to the respective documents:

| Topic                                         | Reference                                                            |

|-----------------------------------------------|----------------------------------------------------------------------|

| Board Update Portal                           | Cyclone IV GX Transceiver Starter Kit User Guide                     |

| PFL Design                                    | Cyclone IV GX Transceiver Starter Kit User Guide                     |

| PFL Megafunction                              | AN 386: Using the Parallel Flash Loader with the Quartus II Software |

| SFL Megafunction                              | AN 370: Using the Serial FlashLoader with the Quartus II Software    |

| Managing and programming EPCS memory contents | Nios II Flash Programmer User Guide                                  |

### **Status Elements**

The starter board includes status LEDs. This section describes the status elements. Table 2–9 lists the LED board references, names, and functional descriptions.

Table 2-9. Board-Specific LEDs

| Board Reference | LED Name                    | Description                                                                                                                                                                                                     |  |

|-----------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D1              | MAX_ERROR                   | Red LED. Illuminates when the MAX II CPLD EPM2210 System Controller fails to configure the FPGA. Driven by the MAX II CPLD EPM2210 System Controller.                                                           |  |

| D2              | CONF_DONE_LED               | Green LED. Illuminates when the FPGA is successfully configured. Driven by the MAX II CPLD EPM2210 System Controller.                                                                                           |  |

| D3, D4          | PROGRAM (PGM_LED1,PGM_LED0) | Green LEDs. Illuminates to show the LED sequence that determines which flash memory image loads to the FPGA when PGM select push-button switch is pressed. Driven by the MAX II CPLD EPM2210 System Controller. |  |

| D12             | Power                       | Blue LED. Illuminates when 9-V – 16-V power is active.                                                                                                                                                          |  |

| D13             | USB_LED                     | Green LED. Illuminates when the embedded USB-Blaster is in use to program the FPGA. Driven by the MAX II CPLD EPM2210 System Controller and MAX IIZ.                                                            |  |

| D14             | ENET_LEDR_TX                | Green LED. Illuminates to indicate Ethernet PHY transmit activity. Dr by the Marvell 88E1111 PHY.                                                                                                               |  |

| D15             | ENET_LEDR_RX                | Green LED. Illuminates to indicate Ethernet PHY receive activity. Driven by the Marvell 88E1111 PHY.                                                                                                            |  |

| D16             | ENET_LEDR_LINK1000          | Green LED. Illuminates to indicate Ethernet linked at 1000 Mbps connection speed. Driven by the Marvell 88E1111 PHY.                                                                                            |  |

| D17             | ENET_LEDR_LINK100           | Green LED. Illuminates to indicate Ethernet linked at 100 Mbps connection speed. Driven by the Marvell 88E1111 PHY.                                                                                             |  |

| D18             | ENET_LEDR_LINK10            | Green LED. Illuminates to indicate Ethernet linked at 10 Mbps connection speed. Driven by the Marvell 88E1111 PHY.                                                                                              |  |

Table 2–10 lists the board-specific LEDs component references and manufacturing information.

Table 2–10.

Board-Specific LEDs Component References and Manufacturing Information

| Board Reference | Description | Manufacturer | Manufacturer Part Number | Manufacturer Website |

|-----------------|-------------|--------------|--------------------------|----------------------|

| D1              | Red LED     | Lumex, Inc.  | SML-LXT0805IW-TR         | www.lumex.com        |

| D2-D4, D13-D18  | Green LEDs  | Lumex, Inc.  | SML-LX1206GC-TR          | www.lumex.com        |

| D12             | Blue LED    | Lumex, Inc.  | SML-LX1206USBC-TR        | www.lumex.com        |

# **Setup Elements**

The starter board includes several different kinds of setup elements. This section describes the following setup elements:

- Board settings DIP switch

- Configuration settings DIP switch

- Configuration push-button switches

### **Board Settings DIP Switch**

The board settings DIP switch (S8) controls various features specific to the board and the MAX II CPLD EPM2210 System Controller logic design. Table 2–11 shows the switch controls and descriptions.

Table 2-11. Board Settings DIP Switch Controls

| Board<br>Reference | Schematic Signal Name | Description                                                   | Default (1) |

|--------------------|-----------------------|---------------------------------------------------------------|-------------|

| S8.1               | CLK_SEL               | ON : On-board 125-MHz LVDS oscillator clock select            | ON          |

|                    |                       | OFF : SMA input clock select                                  |             |

| S8.2               | USER_PGM              | ON: Load user hardware page 1 from flash memory upon power-up | OFF         |

|                    |                       | OFF: Load factory design from flash memory upon power-up      |             |

| \$8.3              | EPM2210_JTAG_EN       | ON: Bypass Max II CPLD EPM2210 System Controller              | OFF         |

|                    |                       | OFF : Max II CPLD EPM2210 System Controller in-chain          |             |

| S8.4               | PCIE_JTAG_EN          | ON : Bypass PCI Express                                       | ON          |

|                    |                       | OFF : PCI Express in-chain                                    |             |

#### Note to Table 2-11:

(1) ON indicates a setting of '0' while OFF indicates a setting of '1'.

Table 2–12 lists the board settings DIP switch component reference and manufacturing information.

**Table 2–12.** Board Settings DIP Switch Component Reference and Manufacturing Information

| Board<br>Reference | Description                    | Manufacturer     | Manufacturer<br>Part Number | Manufacturer Website  |

|--------------------|--------------------------------|------------------|-----------------------------|-----------------------|

| S8                 | Four-position slide DIP switch | C & K Components | TDA04H0SB1                  | www.ck-components.com |

### **Configuration Settings DIP Switch**

The configuration settings DIP switch (S7) controls the configuration scheme selection. A configuration scheme with different configuration voltage standards is selected by driving the MSEL pins either high or low, as shown in Table 2–11.

**Table 2–13.** Configuration Settings DIP Switch Controls (Part 1 of 2) (Note 1)

|                                                           |                  | Setting               |                       |                       |              |  |

|-----------------------------------------------------------|------------------|-----------------------|-----------------------|-----------------------|--------------|--|

| Configuration Scheme                                      | EPCS_nCS (\$7.4) | FPGA_MSEL2<br>(\$7.3) | FPGA_MSEL1<br>(\$7.2) | FPGA_MSEL0<br>(\$7.1) | POR<br>Delay |  |

| Active Serial – Enables active serial                     | 1                | 0                     | 1                     | 1                     | Fast         |  |

| configuration with fast or standard power-on-reset delay. | 1                | 0                     | 1                     | 0                     | Standard     |  |

| Passive Serial – Enables passive serial                   | 0                | 1                     | 0                     | 0                     | Fast         |  |

| configuration with fast or standard power-on-reset delay. | 0                | 0                     | 0                     | 0                     | Standard     |  |

**Table 2–13.** Configuration Settings DIP Switch Controls (Part 2 of 2) (Note 1)

| Configuration Scheme            | EPCS_nCS (\$7.4) | FPGA_MSEL2<br>( <b>\$7.3</b> ) | FPGA_MSEL1 <b>(\$7.2)</b> | FPGA_MSEL0 <b>(\$7.1)</b> | POR<br>Delay |

|---------------------------------|------------------|--------------------------------|---------------------------|---------------------------|--------------|

| JTAG – JTAG-based configuration | X (2)            |                                |                           |                           | _            |

#### Notes to Table 2-13:

- (1) ON indicates a setting of '0' while OFF indicates a setting of '1'.

- (2) X indicates does not care. The JTAG-based configuration takes precedence over other configuration schemes and therefore, the FPGA\_MSEL pin settings are ignored.

Table 2–12 lists the configuration settings DIP switch component reference and manufacturing information.

Table 2–14. Configuration Settings DIP Switch Component Reference and Manufacturing Information

| Board<br>Reference | Description                    | Manufacturer     | Manufacturer<br>Part Number | Manufacturer Website  |

|--------------------|--------------------------------|------------------|-----------------------------|-----------------------|

| S8                 | Four-position slide DIP switch | C & K Components | TDA04H0SB1                  | www.ck-components.com |

### **Configuration Push-Button Switches**

The PGM configure push-button switch, PGM\_CONFIG (S1), is an input to the MAX II CPLD EPM2210 System Controller. The push-button switch forces a reconfiguration of the FPGA from flash memory. The location in the flash memory is based on the PGM\_LED[1:0] setting when the button is released. Valid settings include PGM\_LED0 or PGM\_LED1.

The PGM select push-button switch, PGM\_SEL (S2), toggles the program LEDs (D3, D4) sequence. Refer to Table 2–8 on page 2–11 for the PGM\_LED [1:0] sequence definitions.

The MAX II reset push-button switch, MAX\_RESETn (S3), resets the MAX II CPLD EPM2210 System Controller.

Table 2–15 lists the configuration push-button switches component reference and manufacturing information.

Table 2-15. Configuration Push-button Switches Component Reference and Manufacturing Information

| Board Reference | Description          | Manufacturer | Manufacturer<br>Part Number | Manufacturer Website          |

|-----------------|----------------------|--------------|-----------------------------|-------------------------------|

| S1-S3           | Push-button switches | Panasonic    | EVQPAC07K                   | www.panasonic.com/industrial/ |

# **Clock Circuitry**

This section describes the board's clock inputs.

### **Cyclone IV GX Transceiver Clock Inputs**

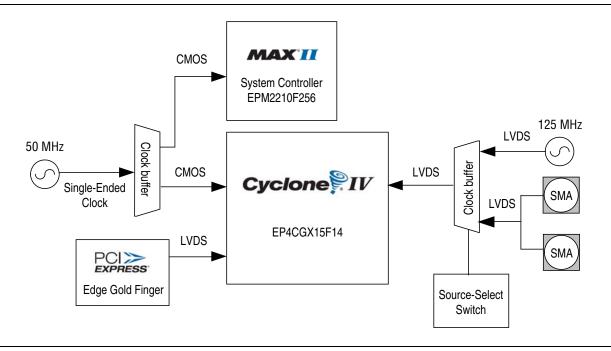

Figure 2–5 shows the Cyclone IV GX Transceiver starter board clock inputs.

Figure 2-5. Cyclone IV GX Transceiver Starter Board Clock Inputs

Table 2–16 shows the clock inputs for the Cyclone IV GX Transceiver starter board.

Table 2-16. Cyclone IV GX Transceiver Starter Board Clock Inputs

| Source<br>Component<br>Board<br>Reference | Source            | Schematic Signal<br>Name | I/O<br>Standard | Cyclone IV GX<br>Device<br>Pin Number | Description                                                       |

|-------------------------------------------|-------------------|--------------------------|-----------------|---------------------------------------|-------------------------------------------------------------------|

| J3                                        | SMA or<br>125 MHz | CLKIN_SMA_P              | LVPECL          | M7 or E7 depending on CLK_SEL         | Positive and negative differential LVPECL clock inputs from SMAs. |

| J2                                        |                   | CLKIN_SMA_N              | LVFEGE          | N7 or E6 depending on CLK_SEL         |                                                                   |

| X1.4                                      |                   | 125M_OCS_P               | LVDS            | M7 or E7 depending on CLK_SEL         | Positive and negative differential LVDS clock inputs from 125-MHz |

| X1.5                                      |                   | 125M_OCS_N               | LVDS            | N7 or E6 depending on CLK_SEL         | crystal oscillator.                                               |

| U14.A13                                   | 100 MHz           | PCIE_REFCLK_P            |                 | J6                                    | Positive and negative differential                                |

| U14.A14                                   |                   | PCIE_REFCLK_N            | HCSL            | J7                                    | HCSL clock inputs from PCI Express edge connector.                |

# **General User Input/Output**

This section describes the user I/O interface to the FPGA, including the push-buttons, DIP switches, status LEDs, and character LCD.

### **User-Defined Push-Button Switches**

The starter board includes three user-defined push-button switches: two general user and one CPU reset push-button switches . For information on the system and safe reset push-button switches, refer to "Configuration Push-Button Switches" on page  $2{\text -}15$ .

Board references S5 and S6 are push-button switches that allow you to interact with the Cyclone IV GX device. When the switch is pressed and held down, the device pin is set to logic 0; when the switch is released, the device pin is set to logic 1. There is no board-specific function for these general user push-button switches.

Board reference S4 is the CPU reset push-button switch, CPU\_RESETn, which is an input to the Cyclone IV GX device and the MAX II CPLD EPM2210 System Controller. CPU\_RESETn is intended to be the master reset signal for the FPGA design loaded into the Cyclone IV GX device. This switch also acts as a regular I/O pin.

Table 2–17 lists the user-defined push-button switch schematic signal names and their corresponding Cyclone IV GX device pin numbers.

**Table 2–17.** User-Defined Push-Button Switch Schematic Signal Names and Functions

| Board Reference | Description                                                           | Schematic Signal<br>Name | I/O Standard | Cyclone IV GX<br>Device Pin Number |

|-----------------|-----------------------------------------------------------------------|--------------------------|--------------|------------------------------------|

| S6              | User-defined push-button switch.                                      | USER_PB0                 |              | H13                                |

| S5              | When the switch is pressed, a logic 0 is selected. When the switch is | USER_PB1                 | 2.5-V        | G13                                |

| S4              | released, a logic 1 is selected.                                      | CPU_RESETn               |              | D10                                |

Table 2–18 lists the user-defined push-button switch component reference and the manufacturing information.

**Table 2–18.** User-Defined Push-Button Switch Component Reference and Manufacturing Information

| <b>Board Reference</b> | Description          | Manufacturer | Manufacturer<br>Part Number | Manufacturer Website          |

|------------------------|----------------------|--------------|-----------------------------|-------------------------------|

| S4 to S6               | Push-button switches | Panasonic    | EVQPAC07K                   | www.panasonic.com/industrial/ |

### **User-Defined LEDs**

The starter board includes four general purpose LEDs. This section describes all user-defined LEDs. For information on board-specific or status LEDs, refer to "Status Elements" on page 2–13.

Board references D5 through D8 are four user-defined LEDs which allow status and debugging signals to be driven to the LEDs from the FPGA designs loaded into the Cyclone IV GX device. The LEDs illuminate when a logic 0 is driven, and turns off when a logic 1 is driven. There is no board-specific function for these LEDs.

Table 2–19 lists the user-defined LED schematic signal names and their corresponding Cyclone IV GX pin numbers.

| Board Reference | Description                             | Schematic<br>Signal Name | I/O Standard | Cyclone IV GX Device<br>Pin Number |

|-----------------|-----------------------------------------|--------------------------|--------------|------------------------------------|

| D8              | User-defined LEDs.                      | USER_LED0                |              | N8                                 |

| D7              | Driving a logic 0 on the I/O port turns | USER_LED1                | 2.5-V        | C13                                |

| D6              | the LED ON. Driving a logic 1 on the    | USER_LED2                | 2.5-V        | N5                                 |

| D5              | I/O port turns the LED OFF.             | USER LED3                |              | M6                                 |

**Table 2–19.** User-Defined LED Schematic Signal Names and Functions

Table 2–20 lists the user-defined LED component reference and the manufacturing information.

Table 2-20. User-Defined LED Component Reference and Manufacturing Information

| Board Reference | Device Description | Manufacturer | Manufacturer Part Number | Manufacturer Website |

|-----------------|--------------------|--------------|--------------------------|----------------------|

| D5 to D8        | Green LEDs         | Lumex, Inc.  | SML-LX1206GC-TR          | www.lumex.com        |

### **LCD**

The starter board contains a single 14-pin 0.1" pitch dual-row header that interfaces to a 16 character  $\times$  2 line Lumex LCD display. The LCD has a 14-pin receptacle that mounts directly to the board's 14-pin header, so it can be easily removed for access to components under the display. You can also use the header for debugging or other purposes.

Table 2–21 summarizes the LCD pin assignments. The signal names and directions are relative to the Cyclone IV GX Transceiver.

**Table 2–21.** LCD Pin Assignments, Schematic Signal Names, and Functions

| Board Reference | Description         | Schematic Signal<br>Name | I/O Standard | Cyclone IV GX<br>Device<br>Pin Number |

|-----------------|---------------------|--------------------------|--------------|---------------------------------------|

| J6.5            | LCD read or write   | FSML_A0                  |              | N4                                    |

| J6.4            | LCD register select | FSML_A1                  |              | A6                                    |

| J6.7            | LCD data bus        | FSML_D0                  |              | D11                                   |

| J6.8            | LCD data bus        | FSML_D1                  |              | D12                                   |

| J6.9            | LCD data bus        | FSML_D2                  |              | E10                                   |

| J6.10           | LCD data bus        | FSML_D3                  | 2.5-V        | F9                                    |

| J6.11           | LCD data bus        | FSML_D4                  |              | E13                                   |

| J6.12           | LCD data bus        | FSML_D5                  |              | F10                                   |

| J6.13           | LCD data bus        | FSML_D6                  |              | F11                                   |

| J6.14           | LCD data bus        | FSML_D7                  |              | G9                                    |

| J6.6            | LCD chip select     | LCD_CSn                  |              | L9                                    |

Table 2–22 shows the LCD pin definitions, and is an excerpt from the Lumex data sheet.

For more information such as timing, character maps, interface guidelines, and other related documentation, visit www.lumex.com.

Pin Number **Symbol Function** Level  $V_{DD}$ Power supply 2  $V_{ss}$ GND (0 V) 3 V<sub>n</sub> For LCD drive 4 RS H/I Register select signal H: Data input L: Instruction input 5 R/W H/L H: Data read (module to MPU) L: Data write (MPU to module) 6 Ε H, H to L 7-14 H/L DB0-DB7 Data bus, software selectable 4-bit or 8-bit mode

Table 2-22. LCD Pin Definitions and Functions

The particular model used does not have a backlight and the LCD drive pin is not connected.

Table 2–23 lists the LCD component references and the manufacturing information.

**Table 2–23.** LCD Component References and Manufacturing Information

| Board<br>Reference | Description                            | Manufacturer | Manufacturer<br>Part Number | Manufacturer<br>Website |

|--------------------|----------------------------------------|--------------|-----------------------------|-------------------------|

| J6                 | 2×7 pin, 100 mil, vertical header      | Samtec       | TSM-107-07-G-D              | www.samtec.com          |

|                    | 2×16 character display, 5×8 dot matrix | Lumex Inc.   | LCM-S01602DSR/C             | www.lumex.com           |

# **Components and Transceiver Interfaces**

This section describes the starter board's communication ports and interface cards relative to the Cyclone IV GX device. The starter board supports the following communication ports:

- PCI Express

- 10/100/1000 Ethernet

- Transceiver SMA connectors (optional)

## **PCI Express**

The Cyclone IV GX Transceiver starter board fits entirely into a PC motherboard with a  $\times 1$  PCI Express slot which can accommodate a half height low-profile PCI Express add-in card. The starter board comes with a full height I/O bracket for its low profile form factor card. This interface uses the Cyclone IV GX device's PCI Express hard IP block, saving logic resources for the user logic application.

For more information on using the PCI Express hard IP block, refer to the PCI Express Compiler User Guide.

The PCI Express interface supports a channel width of  $\times 1$  as well as the connection speed of Gen1 at 2.5 Gbps/lane.

The board's power can be sourced entirely from the PCI Express edge connector when installed into a PC motherboard. Turn the power switch (SW1) to ON position when you install the board into a PC motherboard. Although the board can also be powered by a laptop power supply for use on a lab bench, it is not recommended to use from both supplies at the same time. Ideal diode power sharing devices have been designed into this board to prevent damages or back-current from one supply to the other.

The PCIE\_REFCLK\_P and PCIE\_REFCLK\_N signals are a 100-MHz differential input that is driven from the PC motherboard on this board through the PCI Express edge connector. This signal connects directly to a Cyclone IV GX REFCLK input pin pair. This clock is terminated on the motherboard and therefore, no on-board termination is required. This clock can have spread-spectrum properties that change its period between 9.847 ps to 10.203 ps. The I/O standard is High-Speed Current Steering Logic (HCSL).

By default, the GXB\_RX0 channel of the FPGA is connected to the PCIE\_RX\_P and PCIE\_RX\_N signals, while the GXB\_TX0 channel is connected to the PCIE\_TX\_P and PCIE\_TX\_N signals.

Table 2–24 summarizes the PCI Express pin assignments. The signal names and directions are relative to the Cyclone IV GX FPGA.

**Table 2–24.** PCI Express Pin Assignments, Schematic Signal Names, and Functions

| Board Reference | Description                 | Schematic Signal Name | I/O Standard | Cyclone IV GX<br>Device<br>Pin Number |

|-----------------|-----------------------------|-----------------------|--------------|---------------------------------------|

| U14.A16         | Add-in card transmit bus    | PCIE_TX_P             |              | G2                                    |

| U14.A17         | Add-in card transmit bus    | PCIE_TX_N             | 1 4 V DOM    | G1                                    |

| U14.B14         | Add-in card receive bus     | PCIE_RX_P             | 1.4-V PCML   | J2                                    |

| U14.B15         | Add-in card receive bus     | PCIE_RX_N             |              | J1                                    |

| U14.A13         | Motherboard reference clock | PCIE_REFCLK_P         | HCSL         | J6                                    |

| U14.A14         | Motherboard reference clock | PCIE_REFCLK_N         | HUSL         | J7                                    |

| U14.A11         | Reset                       | PCIE_PERSTn           | LVTTL        | A10                                   |

| U14.A1          | Present                     | PCIE_PRSNTn_x1        | <del>_</del> | _                                     |

| U14.B17         | x1 Present                  | PCIE_PRSNTn_x1        | _            | _                                     |

| U14.A5          | Motherboard TCK             | PCIE_JTAG_TCK         |              | _                                     |

| U14.A6          | Motherboard TDI             | PCIE_JTAG_TDI         | 3.3-V        | _                                     |

| U14.A7          | Motherboard TDO             | PCIE_JTAG_TDO         | J.J-V        | _                                     |

| U14.A8          | Motherboard TMS             | PCIE_JTAG_TMS         |              | _                                     |

### 10/100/1000 Ethernet

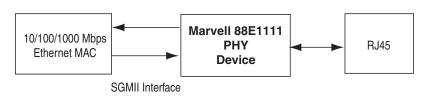

A Marvell 88E1111 PHY device is used for 10/100/1000 BASE-T Ethernet connection. The device is an auto-negotiating Ethernet PHY with an SGMII interface to the FPGA. The MAC function must be provided in the FPGA for typical networking applications such the Altera Triple Speed Ethernet MegaCore design. The Marvell 88E1111 PHY uses 2.5-V and 1.2-V power rails and requires a 25-MHz reference clock driven from a dedicated oscillator. The device interfaces to a Halo Electronics HFJ11-1G02E model RJ45 with internal magnetics that can be used for driving copper lines with Ethernet traffic.

By default, the GXB\_RX1 and GXB\_TX1 channels of the FPGA are connected to the Ethernet PHY as shown in Table 2–27 on page 2–22.

Figure 2–6 shows the SGMII interface between the FPGA (MAC) and Marvell 88E1111 PHY.

Figure 2-6. SGMII Interface between FPGA (MAC) and Marvell 88E1111 PHY

Table 2–25 lists the Ethernet PHY interface pin assignments.

**Table 2–25.** Ethernet PHY Pin Assignments, Signal Names and Functions

| Board Reference | Description              | Schematic Signal Name | I/O Standard | Cyclone IV GX<br>Device<br>Pin Number |

|-----------------|--------------------------|-----------------------|--------------|---------------------------------------|

| U9.82           | SGMII TX data            | ENET_TX_P             |              | C2                                    |

| U9.81           | SGMII TX data            | ENET_TX_N             | 1.4-V PCML   | C1                                    |

| U9.77           | SGMII RX data            | ENET_RX_P             | 1.4-V FOIVIL | E2                                    |

| U9.75           | SGMII RX data            | ENET_RX_N             |              | E1                                    |

| U9.25           | Management bus control   | ENET_MDC              |              | N9                                    |

| U9.24           | Management bus data      | ENET_MDIO             | 2.5-V        | K8                                    |

| U9.23           | Management bus interrupt | ENET_INTn             | 2.J-V        | F12                                   |

| U9.28           | Device reset             | ENET_RESETn           |              | K9                                    |

Table 2–26 lists the Ethernet PHY interface component reference and manufacturing information.

**Table 2–26.** Ethernet PHY Component Reference and Manufacturing Information

| Board<br>Reference | Description                | Manufacturer          | Manufacturing<br>Part Number | Manufacturer<br>Website |

|--------------------|----------------------------|-----------------------|------------------------------|-------------------------|

| U9                 | Ethernet PHY BASE-T device | Marvell Semiconductor | 88E1111-B2-CAAIC000          | www.marvell.com         |

### Transceiver SMA Connectors (Optional)

Board references J9 and J8 are two optional input SMAs to the high-speed positive and negative differential receiver channel while J11 and J10 are two optional output SMAs from the high-speed positive and negative differential transmitter channel. By default, the GXB\_RX1 channel of the FPGA is connected to the Ethernet PHY through capacitor multiplexer C59 and C58, while the GXB\_TX1 channel is connected to the Ethernet PHY through resistor multiplexer R53 and R52. You need to perform a solder modification on the board if you intend to use the optional transceiver SMA connectors. You can use these SMAs to connect to external circuit boards or daughtercards for transceiver applications.

Table 2–27 shows the capacitor and resistor multiplexer locations to enable either the default Ethernet PHY connection or the optional transceiver SMA connectors. The capacitors multiplexer are 0.1- $\mu$ F capacitors and the multiplexer resistors are 0- $\Omega$  resistors.