# *CC1020* Low-Power RF Transceiver for Narrowband Systems

# Applications

- Narrowband low power UHF wireless data transmitters and receivers with channel spacing as low as 12.5 and 25 kHz

- 402 / 424 / 426 / 429 / 433 / 447 / 449 / 469 / 868 / 915 / 960 MHz ISM/SRD band systems

# **Product Description**

**CC1020** is a true single-chip UHF transceiver designed for very low power and very low voltage wireless applications. The circuit is mainly intended for the ISM (Industrial, Scientific and Medical) and SRD (Short Range Device) frequency bands at 402, 424, 426, 429, 433, 447, 449, 469, 868, 915, and 960 MHz, but can easily be programmed for multi-channel operation at other frequencies in the 402 -470 and 804 - 960 MHz range.

The *CC1020* is especially suited for narrowband systems with channel spacing of 12.5 or 25 kHz complying with ARIB STD-T67 and EN 300 220.

## Features

- True single chip UHF RF transceiver

- Frequency range 402 MHz 470 MHz and 804 MHz 960 MHz

- High sensitivity (up to -118 dBm for a 12.5 kHz channel)

- Programmable output power

- Low current consumption (RX: 19.9 mA)

- Low supply voltage (2.3 V to 3.6 V)

- No external IF filter needed

- Low-IF receiver

- Very few external components required

- Small size (QFN 32 package)

- Pb-free package

- Digital RSSI and carrier sense indicator

- Data rate up to 153.6 kBaud

- AMR Automatic Meter Reading

- Wireless alarm and security systems

- Home automation

- Low power telemetry

The **CC1020** main operating parameters can be programmed via a serial bus, thus making **CC1020** a very flexible and easy to use transceiver.

In a typical system *CC1020* will be used together with a microcontroller and a few external passive components.

- OOK, FSK and GFSK data modulation

- Integrated bit synchronizer

- Image rejection mixer

- Programmable frequency and AFC make crystal temperature drift compensation possible without TCXO

- Suitable for frequency hopping systems

- Suited for systems targeting compliance with EN 300 220, FCC CFR47 part 15, ARIB STD-T67, and ARIB STD-T96

- Development kit available

- Easy-to-use software for generating the **CC1020** configuration data

TI recommends using the latest RF performance line device CC1120 as successor of CC1020: <u>www.ti.com/rfperformanceline</u>"

# **Table of Contents**

| 1.  | Abbre   | viations                                                       | 4  |

|-----|---------|----------------------------------------------------------------|----|

| 2.  | Absol   | ute Maximum Ratings                                            | 5  |

| 3.  | Opera   | ting Conditions                                                | 5  |

| 4.  | Electri | ical Specifications                                            | 5  |

|     | 4.1.    | RF Transmit Section                                            | 6  |

|     | 4.2.    | RF Receive Section                                             | 8  |

|     | 4.3.    | RSSI / Carrier Sense Section                                   | 11 |

|     | 4.4.    | IF Section                                                     | 11 |

|     | 4.5.    | Crystal Oscillator Section                                     | 12 |

|     | 4.6.    | Frequency Synthesizer Section                                  | 13 |

|     | 4.7.    | Digital Inputs / Outputs                                       | 14 |

|     | 4.8.    | Current Consumption                                            | 15 |

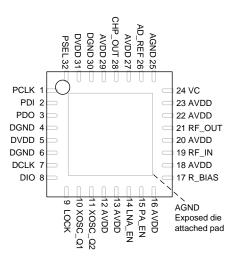

| 5.  | Pin As  | signment                                                       | 15 |

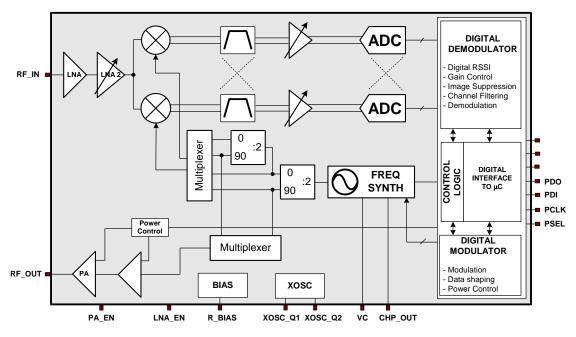

| 6.  | Circuit | t Description                                                  | 17 |

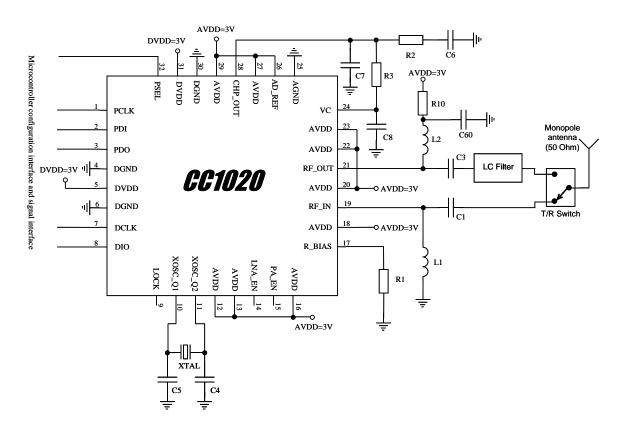

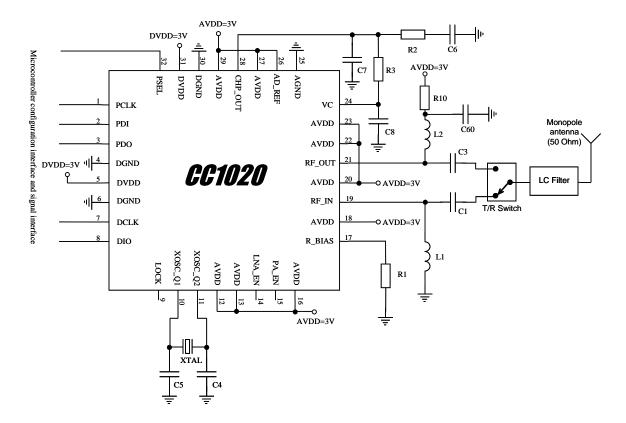

| 7.  | Applic  | ation Circuit                                                  | 18 |

| 8.  | Config  | guration Overview                                              | 21 |

|     | 8.1.    | Configuration Software                                         | 21 |

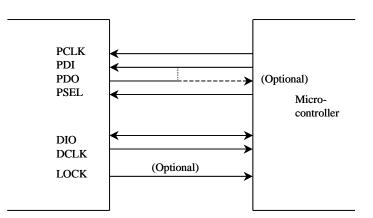

| 9.  | Micro   | controller Interface                                           | 22 |

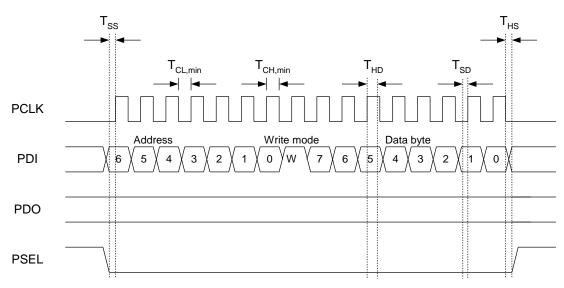

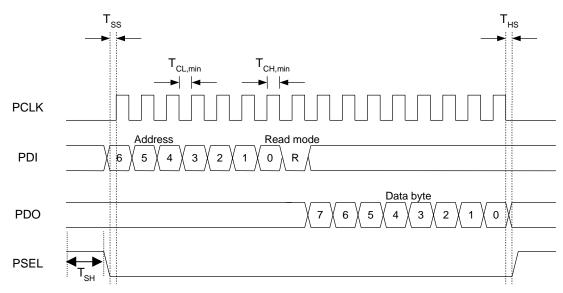

|     | 9.1.    | 4-wire Serial Configuration Interface                          | 23 |

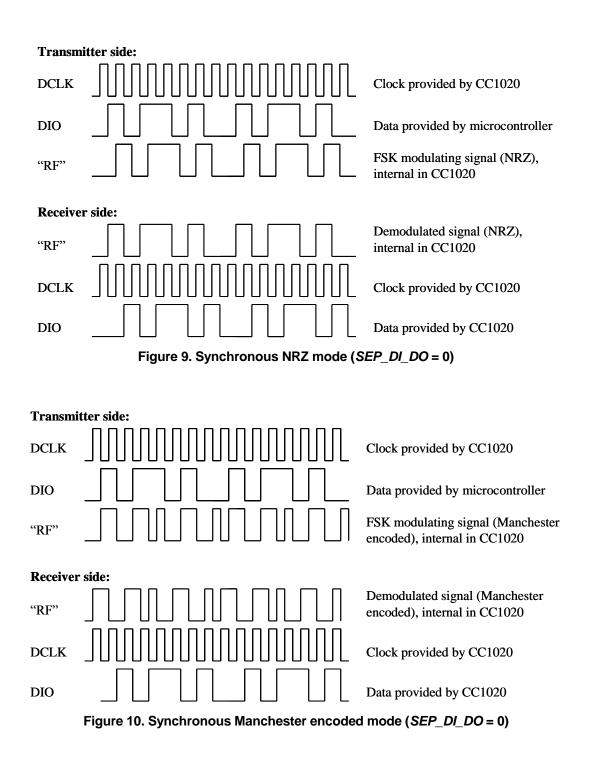

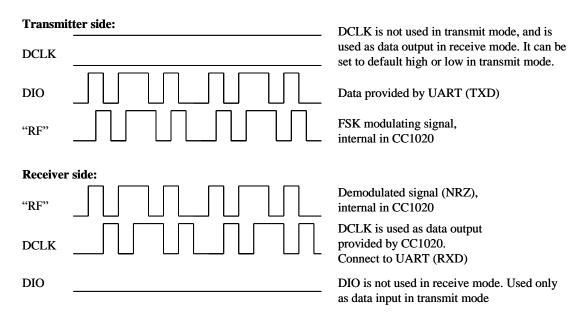

|     | 9.2.    | Signal Interface                                               | 25 |

| 10. | Data R  | Rate Programming                                               | 27 |

| 11. | Freque  | ency Programming                                               | 28 |

|     | 11.1.   | Dithering                                                      | 29 |

| 12. | Receiv  | /er                                                            | 30 |

|     | 12.1.   | IF Frequency                                                   | 30 |

|     | 12.2.   | Receiver Channel Filter Bandwidth                              | 30 |

|     | 12.3.   | Demodulator, Bit Synchronizer and Data Decision                | 31 |

|     | 12.4.   | Receiver Sensitivity versus Data Rate and Frequency Separation | 32 |

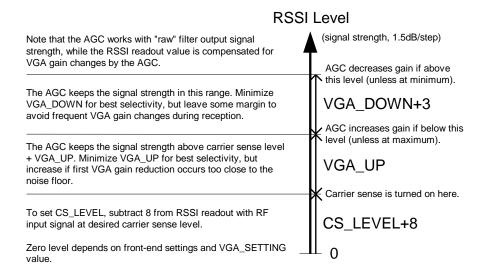

|     | 12.5.   | RSSI                                                           | 33 |

|     | 12.6.   | Image Rejection Calibration                                    | 35 |

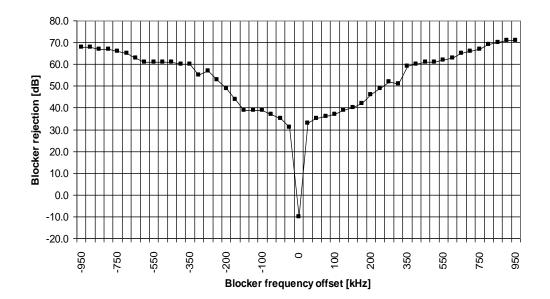

|     | 12.7.   | Blocking and Selectivity                                       | 36 |

|     | 12.8.   | Linear IF Chain and AGC Settings                               | 37 |

|     | 12.9.   | AGC Settling                                                   | 38 |

|     | 12.10.  | Preamble Length and Sync Word                                  | 39 |

|     | 12.11.  | Carrier Sense                                                  | 39 |

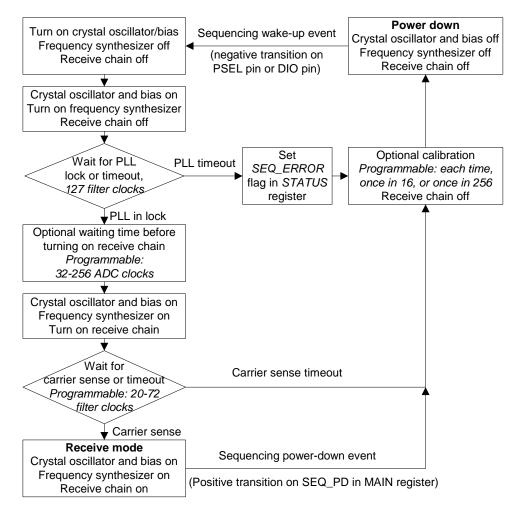

|     | 12.12.  | Automatic Power-up Sequencing                                  | 40 |

|     | 12.13.  | Automatic Frequency Control                                    | 41 |

|     | 12.14.  | Digital FM                                                     | 42 |

| 13. | Transn   | nitter                                              | 43 |

|-----|----------|-----------------------------------------------------|----|

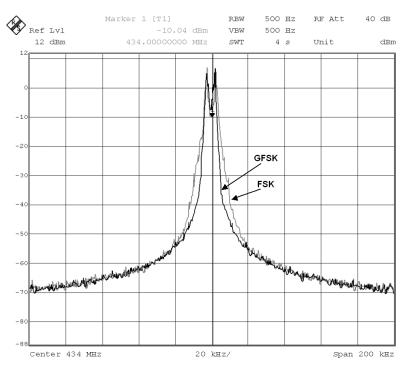

|     | 13.1.    | FSK Modulation Formats                              | 43 |

|     | 13.2.    | Output Power Programming                            | 45 |

|     | 13.3.    | TX Data Latency                                     | 46 |

|     | 13.4.    | Reducing Spurious Emission and Modulation Bandwidth | 46 |

| 14. | Input /  | Output Matching and Filtering                       | 46 |

| 15. | Freque   | ncy Synthesizer                                     | 50 |

|     | 15.1.    | VCO, Charge Pump and PLL Loop Filter                | 50 |

|     | 15.2.    | VCO and PLL Self-Calibration                        | 51 |

|     | 15.3.    | PLL Turn-on Time versus Loop Filter Bandwidth       | 52 |

|     | 15.4.    | PLL Lock Time versus Loop Filter Bandwidth          | 53 |

| 16. | VCO ai   | nd LNA Current Control                              | 53 |

| 17. | Power    | Management                                          | 54 |

| 18. | On-Off   | Keying (OOK)                                        | 57 |

| 19. | Crysta   | I Oscillator                                        | 58 |

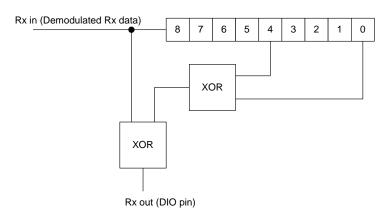

| 20. | Built-ir | n Test Pattern Generator                            | 59 |

| 21. | Interru  | pt on Pin DCLK                                      | 60 |

|     | 21.1.    | Interrupt upon PLL Lock                             | 60 |

|     | 21.2.    | Interrupt upon Received Signal Carrier Sense        | 60 |

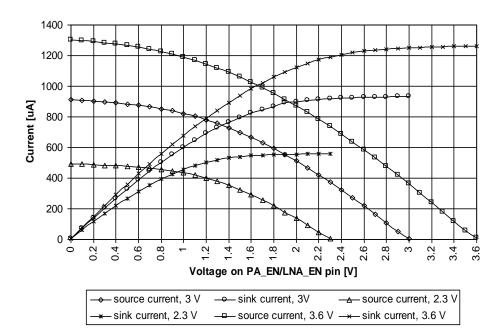

| 22. | PA_EN    | and LNA_EN Digital Output Pins                      | 61 |

|     | 22.1.    | Interfacing an External LNA or PA                   | 61 |

|     | 22.2.    | General Purpose Output Control Pins                 | 61 |

|     | 22.3.    | PA_EN and LNA_EN Pin Drive                          | 61 |

| 23. | Systen   | n Considerations and Guidelines                     | 62 |

| 24. | PCB La   | ayout Recommendations                               | 64 |

| 25. | Antenr   | a Considerations                                    | 65 |

| 26. | Config   | uration Registers                                   | 65 |

|     | 26.1.    | CC1020 Register Overview                            | 66 |

| 27. | Packag   | ge Marking                                          | 86 |

| 28. | Solder   | ing Information                                     | 86 |

| 29. | Plastic  | Tube Specification                                  | 86 |

| 30. | Orderi   | ng Information                                      | 87 |

| 31. | Genera   | al Information                                      | 88 |

# *CC1020*

# 1. Abbreviations

| ACP<br>ACR<br>ADC<br>AFC<br>AGC<br>AMR<br>ASK<br>BER<br>BOM<br>bps<br>BT<br>ChBW<br>CW<br>DAC<br>DNM<br>ESR<br>FHSS<br>FM<br>FS<br>FSK<br>GFSK<br>IC<br>IF<br>IP3<br>ISM<br>kbps<br>LNA<br>LO<br>MCU<br>NRZ<br>OOK<br>PA<br>PD<br>PER<br>PCB<br>PN9<br>PLL<br>PSEL<br>RF<br>RSSI<br>RX<br>SBW<br>SPI<br>SRD<br>TBD<br>T/R | Adjacent Channel Power<br>Adjacent Channel Rejection<br>Analog-to-Digital Converter<br>Automatic Frequency Control<br>Automatic Gain Control<br>Automatic Meter Reading<br>Amplitude Shift Keying<br>Bit Error Rate<br>Bill Of Materials<br>bits per second<br>Bandwidth-Time product (for GFSK)<br>Receiver Channel Filter Bandwidth<br>Continuous Wave<br>Digital-to-Analog Converter<br>Do Not Mount<br>Equivalent Series Resistance<br>Frequency Hopping Spread Spectrum<br>Frequency Modulation<br>Frequency Synthesizer<br>Frequency Synthesizer<br>Frequency Shift Keying<br>Gaussian Frequency Shift Keying<br>Integrated Circuit<br>Intermediate Frequency<br>Third Order Intercept Point<br>Industrial Scientific Medical<br>kilo bits per second<br>Low Noise Amplifier<br>Local Oscillator (in receive mode)<br>Micro Controller Unit<br>Non Return to Zero<br>On-Off Keying<br>Power Amplifier<br>Phase Detector / Power Down<br>Packet Error Rate<br>Printed Circuit Board<br>Pseudo-random Bit Sequence (9-bit)<br>Phase Locked Loop<br>Program Select<br>Radio Frequency<br>Received Signal Strength Indicator<br>Receive (mode)<br>Signal Bandwidth<br>Serial Peripheral Interface<br>Short Range Device<br>To Be Decided/Defined<br>Transmit/Receive (switch) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI                                                                                                                                                                                                                                                                                                                       | Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SRD                                                                                                                                                                                                                                                                                                                       | Short Range Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TBD                                                                                                                                                                                                                                                                                                                       | To Be Decided/Defined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| T/R                                                                                                                                                                                                                                                                                                                       | Transmit/Receive (switch)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TX                                                                                                                                                                                                                                                                                                                        | Transmit (mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| UHF                                                                                                                                                                                                                                                                                                                       | Ultra High Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VCO                                                                                                                                                                                                                                                                                                                       | Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VGA                                                                                                                                                                                                                                                                                                                       | Variable Gain Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XOSC                                                                                                                                                                                                                                                                                                                      | Crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| XTAL                                                                                                                                                                                                                                                                                                                      | Crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# 2. Absolute Maximum Ratings

The absolute maximum ratings given Table 1 should under no circumstances be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

| Parameter                 | Min  | Max              | Unit | Condition                                     |

|---------------------------|------|------------------|------|-----------------------------------------------|

| Supply voltage, VDD       | -0.3 | 5.0              | V    | All supply pins must have the<br>same voltage |

| Voltage on any pin        | -0.3 | VDD+0.3, max 5.0 | V    |                                               |

| Input RF level            |      | 10               | dBm  |                                               |

| Storage temperature range | -50  | 150              | °C   |                                               |

| Package body temperature  |      | 260              | °C   | Norm: IPC/JEDEC J-STD-020 1                   |

| Humidity non-condensing   | 5    | 85               | %    |                                               |

| ESD                       |      | ±1               | kV   | All pads except RF                            |

| (Human Body Model)        |      | ±0.4             | kV   | RF Pads                                       |

#### Table 1. Absolute maximum ratings

<sup>1</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD\_020"Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices".

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

# 3. Operating Conditions

The operating conditions for *CC1020* are listed in Table 2.

| Parameter                           | Min        | Тур | Max        | Unit       | Condition / Note                                                                                                                                                                                                      |

|-------------------------------------|------------|-----|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF Frequency Range                  | 402<br>804 |     | 470<br>960 | MHz<br>MHz | Programmable in <300 Hz steps<br>Programmable in <600 Hz steps                                                                                                                                                        |

| Operating ambient temperature range | -40        |     | 85         | °C         |                                                                                                                                                                                                                       |

| Supply voltage                      | 2.3        | 3.0 | 3.6        | V          | The same supply voltage should<br>be used for digital (DVDD) and<br>analog (AVDD) power.<br>A 3.0 ±0.1 V supply is<br>recommended to meet the ARIB<br>STD-T67 selectivity and output<br>power tolerance requirements. |

| Table 2. | Operating | conditions |

|----------|-----------|------------|

|----------|-----------|------------|

## 4. Electrical Specifications

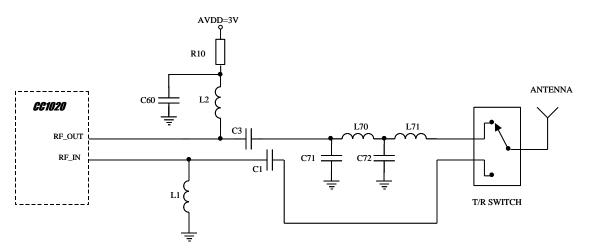

Table 3 to Table 10 gives the **CC1020** electrical specifications. All measurements were performed using the 2 layer PCB CC1020EMX reference design. This is the same test circuit as shown in Figure 3. Temperature =  $25^{\circ}$ C, supply voltage = AVDD = DVDD = 3.0 V if nothing else stated. Crystal frequency = 14.7456 MHz.

The electrical specifications given for 868 MHz are also applicable for the 902 - 928 MHz frequency range.

# 4.1. RF Transmit Section

| Parameter                                                                                | Min    | Тур        | Max        | Unit       | Condition / Note                                                                                                                                                                    |

|------------------------------------------------------------------------------------------|--------|------------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit data rate                                                                       | 0.45   |            | 153.6      | kBaud      | The data rate is programmable.<br>See section 10 on page 27 for<br>details.                                                                                                         |

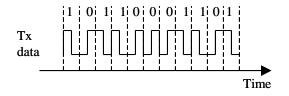

|                                                                                          |        |            |            |            | NRZ or Manchester encoding can<br>be used. 153.6 kBaud equals<br>153.6 kbps using NRZ coding<br>and 76.8 kbps using Manchester<br>coding. See section 9.2 on page<br>25 for details |

|                                                                                          |        |            |            |            | Minimum data rate for OOK is 2.4<br>kBaud                                                                                                                                           |

| Binary FSK frequency separation                                                          | 0<br>0 |            | 108<br>216 | kHz<br>kHz | in 402 - 470 MHz range<br>in 804 - 960 MHz range                                                                                                                                    |

|                                                                                          |        |            |            |            | 108/216 kHz is the maximum<br>specified separation at 1.84 MHz<br>reference frequency. Larger<br>separations can be achieved at<br>higher reference frequencies.                    |

| Output power                                                                             |        |            |            |            | Delivered to 50 $\Omega$ single-ended load. The output power is                                                                                                                     |

| 433 MHz                                                                                  |        | -20 to +10 |            | dBm        | programmable and should not be<br>programmed to exceed +10/+5                                                                                                                       |

| 868 MHz                                                                                  |        | -20 to +5  |            | dBm        | dBm at 433/868 MHz under any<br>operating conditions (refer to<br>CC1020 Errata Note 003). See<br>section 14 on page 46 for details.                                                |

| Output power tolerance                                                                   |        | -4<br>+3   |            | dB<br>dB   | At maximum output power<br>At 2.3 V, +85°C<br>At 3.6 V, -40°C                                                                                                                       |

| Harmonics, radiated CW                                                                   |        |            |            |            | Harmonics are measured as                                                                                                                                                           |

| 2 <sup>nd</sup> harmonic, 433 MHz, +10 dBm<br>3 <sup>rd</sup> harmonic, 433 MHz, +10 dBm |        | -50<br>-50 |            | dBc<br>dBc | EIRP values according to EN 300<br>220. The antenna (SMAFF-433<br>and SMAFF-868 from R.W.                                                                                           |

| 2 <sup>nd</sup> harmonic, 868 MHz, +5 dBm<br>3 <sup>rd</sup> harmonic, 868 MHz, +5 dBm   |        | -50<br>-50 |            | dBc<br>dBc | Badland) plays a part in attenuating the harmonics.                                                                                                                                 |

| Adjacent channel power (GFSK)                                                            |        |            |            |            | For 12.5 kHz channel spacing                                                                                                                                                        |

| 12.5 kHz channel spacing, 433 MHz                                                        |        | -46        |            | dBc        | ACP is measured in a ±4.25 kHz<br>bandwidth at ±12.5 kHz offset.                                                                                                                    |

| 25 kHz channel spacing, 433 MHz                                                          |        | -52        |            | dBc        | Modulation: 2.4 kBaud NRZ PN9<br>sequence, ±2.025 kHz frequency<br>deviation.                                                                                                       |

| 25 kHz channel spacing, 868 MHz                                                          |        | -49        |            | dBc        | For 25 kHz channel spacing ACP<br>is measured in a ±8.5 kHz<br>bandwidth at ±25 kHz offset.<br>Modulation: 4.8 kBaud NRZ PN9<br>sequence, ±2.475 kHz frequency<br>deviation.        |

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                       | Min | Тур                            | Мах               | Unit                                          | Condition / Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|-------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Occupied bandwidth (99.5%,GFSK)         12.5 kHz channel spacing, 433 MHz         25 kHz channel spacing, 433 MHz         25 kHz channel spacing, 868 MHz         Modulation bandwidth, 868 MHz         19.2 kBaud, ±9.9 kHz frequency deviation         38.4 kBaud, ±19.8 kHz frequency deviation         Spurious emission, radiated CW         47-74, 87.5-118, 174-230, 470-862 MHz         9 kHz - 1 GHz         1 - 4 GHz |     | 7.5<br>9.6<br>9.6<br>48<br>106 | -54<br>-36<br>-30 | kHz<br>kHz<br>kHz<br>kHz<br>dBm<br>dBm<br>dBm | Bandwidth for 99.5% of total<br>average power.<br>Modulation for 12.5 channel<br>spacing: 2.4 kBaud NRZ PN9<br>sequence, ±2.025 kHz frequency<br>deviation.<br>Modulation for 25 kHz channel<br>spacing: 4.8 kBaud NRZ PN9<br>sequence, ±2.475 kHz frequency<br>deviation.<br>Bandwidth where the power<br>envelope of modulation equals<br>-36 dBm. Spectrum analyzer<br>RBW = 1 kHz.<br>At maximum output power,<br>+10/+5 dBm at 433/868 MHz.<br>To comply with EN 300 220,<br>FCC CFR47 part 15, ARIB STD-<br>T67, and ARIB STD-T96 an<br>external (antenna) filter, as<br>implemented in the application<br>circuit in Figure 25, must be used<br>and tailored to each individual<br>design to reduce out-of-band<br>spurious emissions can be<br>measured as EIRP values<br>according to EN 300 220. The<br>antenna (SMAFF-433 and<br>SMAFF-868 from R.W. Badland)<br>plays a part in attenuating the<br>spurious emissions.<br>If the output power is increased<br>using an external PA, a filter must<br>be used to attenuate spurs below<br>862 MHz when operating in the<br>868 MHz frequency band in<br>Europe. Application Note <i>AN036</i><br><i>CC1020/1021 Spurious Emission</i> |

| Optionum land importance                                                                                                                                                                                                                                                                                                                                                                                                        |     |                                |                   |                                               | presents and discusses a solution<br>that reduces the TX mode<br>spurious emission close to 862<br>MHz by increasing the REF_DIV<br>from 1 to 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Optimum load impedance                                                                                                                                                                                                                                                                                                                                                                                                          |     |                                |                   |                                               | Transmit mode. For matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 433 MHz                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 54 + j44                       |                   | Ω                                             | details see section 14 on page 46.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 868 MHz                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 15 + j24                       |                   | Ω                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 915 MHz                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 20 + j35                       |                   | Ω                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Table 3. RF transmit parameters

# 4.2. RF Receive Section

| Parameter                                                                   | Min | Тур                | Max | Unit              | Condition / Note                                                                                                                           |

|-----------------------------------------------------------------------------|-----|--------------------|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Sensitivity, 433 MHz, FSK                                          |     |                    |     |                   | Sensitivity is measured with PN9 sequence at BER = $10^{-3}$                                                                               |

| 12.5 kHz channel spacing, optimized selectivity, ±2.025 kHz freq. deviation |     | -114               |     | dBm               | 12.5 kHz channel spacing:<br>2.4 kBaud, Manchester coded                                                                                   |

| 12.5 kHz channel spacing, optimized sensitivity, ±2.025 kHz freq. deviation |     | -118               |     | dBm               | data.                                                                                                                                      |

| 25 kHz channel spacing                                                      |     | -112               |     | dBm               | 25 kHz channel spacing:<br>4.8 kBaud, NRZ coded data,<br>±2.475 kHz frequency deviation.                                                   |

| 500 kHz channel spacing                                                     |     | -96                |     | dBm               | 500 kHz channel spacing:<br>153.6 kBaud, NRZ coded data,<br>±72 kHz frequency deviation.                                                   |

| Receiver Sensitivity, 868 MHz, FSK                                          |     |                    |     |                   |                                                                                                                                            |

| 12.5 kHz channel spacing, ±2.475 kHz freq. deviation                        |     | -116               |     | dBm               | See Table 19 and Table 20 for typical sensitivity figures at other data rates.                                                             |

| 25 kHz channel spacing                                                      |     | -111               |     | dBm               |                                                                                                                                            |

| 500 kHz channel spacing                                                     |     | -94                |     | dBm               |                                                                                                                                            |

| Receiver sensitivity, 433 MHz, OOK                                          |     |                    |     |                   | Sensitivity is measured with PN9                                                                                                           |

| 2.4 kBaud<br>153.6 kBaud                                                    |     | -116<br>-81        |     | dBm<br>dBm        | sequence at BER = 10 <sup>-3</sup><br>Manchester coded data.                                                                               |

| Receiver sensitivity, 868 MHz, OOK                                          |     |                    |     |                   | See Table 27 for typical                                                                                                                   |

| 4.8 kBaud<br>153.6 kBaud                                                    |     | -107<br>-87        |     | dBm<br>dBm        | sensitivity figures at other data rates.                                                                                                   |

| Saturation (maximum input level)<br>FSK and OOK                             |     | 10                 |     | dBm               | FSK: Manchester/NRZ coded<br>data<br>OOK: Manchester coded data<br>BER = 10 <sup>-3</sup>                                                  |

| System noise bandwidth                                                      |     | 9.6<br>to<br>307.2 |     | kHz               | The receiver channel filter 6 dB<br>bandwidth is programmable from<br>9.6 kHz to 307.2 kHz. See<br>section 12.2 on page 30 for<br>details. |

| Noise figure, cascaded<br>433 and 868 MHz                                   |     | 7                  |     | dB                | NRZ coded data                                                                                                                             |

| Input IP3                                                                   |     |                    |     |                   | Two tone test (+10 MHz and +20 MHz)                                                                                                        |

| 433 MHz, 12.5 kHz channel spacing                                           |     | -23<br>-18<br>-16  |     | dBm<br>dBm<br>dBm | LNA2 maximum gain<br>LNA2 medium gain<br>LNA2 minimum gain                                                                                 |

| 868 MHz, 25 kHz channel spacing                                             |     | -18<br>-15<br>-13  |     | dBm<br>dBm<br>dBm | LNA2 maximum gain<br>LNA2 medium gain<br>LNA2 minimum gain                                                                                 |

| Parameter                                                                                                                                | Min | Тур                              | Max | Unit                 | Condition / Note                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Co-channel rejection, FSK and OOK                                                                                                        |     |                                  |     |                      |                                                                                                                                                                                                                                                                                               |

| 12.5 kHz channel spacing, 433 MHz                                                                                                        |     | -11                              |     | dB                   | Wanted signal 3 dB above the sensitivity level, FM jammer (1                                                                                                                                                                                                                                  |

| 25 kHz channel spacing, 433 MHz                                                                                                          |     | -11                              |     | dB                   | kHz sine, $\pm$ 2.5 kHz deviation) at operating frequency,<br>BER = $10^{-3}$                                                                                                                                                                                                                 |

| 25 kHz channel spacing, 868 MHz                                                                                                          |     | -11                              |     | dB                   | DER = 10                                                                                                                                                                                                                                                                                      |

| Adjacent channel rejection (ACR)                                                                                                         |     |                                  |     |                      | Wanted signal 2 dB above the                                                                                                                                                                                                                                                                  |

| 12.5 kHz channel spacing, 433 MHz                                                                                                        |     | 32                               |     | dB                   | Wanted signal 3 dB above the<br>sensitivity level, FM jammer (1<br>kHz sine, ± 2.5 kHz deviation) at                                                                                                                                                                                          |

| 25 kHz channel spacing, 433 MHz                                                                                                          |     | 37                               |     | dB                   | adjacent channel. BER = $10^{-3}$                                                                                                                                                                                                                                                             |

| 25 kHz channel spacing, 868 MHz                                                                                                          |     | 32                               |     | dB                   |                                                                                                                                                                                                                                                                                               |

| Image channel rejection<br>433/868 MHz                                                                                                   |     |                                  |     |                      | Wanted signal 3 dB above the                                                                                                                                                                                                                                                                  |

| No I/Q gain and phase calibration                                                                                                        |     | 26/31                            |     | dB                   | sensitivity level, CW jammer at image frequency. BER = 10 <sup>-3</sup> .                                                                                                                                                                                                                     |

| I/Q gain and phase calibrated                                                                                                            |     | 49/52                            |     | dB                   | Image rejection after calibration<br>will depend on temperature and<br>supply voltage. Refer to section<br>12.6 on page 35.                                                                                                                                                                   |

| Selectivity*                                                                                                                             |     |                                  |     |                      |                                                                                                                                                                                                                                                                                               |

| 12.5 kHz channel spacing, 433 MHz                                                                                                        |     | 41                               |     | dB                   | Wanted signal 3 dB above the sensitivity level. CW jammer is                                                                                                                                                                                                                                  |

| 25 kHz channel spacing, 433 MHz                                                                                                          |     | 41                               |     | dB                   | swept in 12.5 kHz/25 kHz steps<br>to within $\pm$ 1 MHz from wanted<br>channel. BER = $10^{-3}$ . Adjacent                                                                                                                                                                                    |

| 25 kHz channel spacing, 868 MHz                                                                                                          |     | 39                               |     | dB                   | channel and image channel are<br>excluded.                                                                                                                                                                                                                                                    |

| (*Close-in spurious response rejection)                                                                                                  |     |                                  |     |                      | excluded.                                                                                                                                                                                                                                                                                     |

| Blocking / Desensitization*<br>433/868 MHz<br>± 1 MHz<br>± 2 MHz<br>± 5 MHz<br>± 10 MHz<br>(*Out-of-band spurious response<br>rejection) |     | 50/57<br>64/71<br>64/71<br>75/78 |     | dB<br>dB<br>dB<br>dB | Wanted signal 3 dB above the<br>sensitivity level, CW jammer at $\pm$<br>1, 2, 5 and 10 MHz offset.<br>BER = 10 <sup>-3</sup> . 12.5 kHz/25 kHz<br>channel spacing at 433/868 MHz.<br>Complying with EN 300 220,<br>class 2 receiver requirements.                                            |

| Image frequency suppression,<br>433/868 MHz                                                                                              |     |                                  |     |                      | Ratio between sensitivity for a signal at the image frequency to                                                                                                                                                                                                                              |

| No I/Q gain and phase calibration                                                                                                        |     | 36/41                            |     | dB                   | the sensitivity in the wanted<br>channel. Image frequency is RF-                                                                                                                                                                                                                              |

| I/Q gain and phase calibrated                                                                                                            |     | 59/62                            |     | dB                   | 2 IF. The signal source is a 2.4 kBaud, Manchester coded data, $\pm 2.025$ kHz frequency deviation, signal level for BER = $10^{-3}$                                                                                                                                                          |

| Spurious reception                                                                                                                       | 40  |                                  |     | dB                   | Ratio between sensitivity for an<br>unwanted frequency to the<br>sensitivity in the wanted channel.<br>The signal source is a 2.4 kBaud,<br>Manchester coded data, $\pm 2.025$<br>kHz frequency deviation, swept<br>over all frequencies 100 MHz - 2<br>GHz. Signal level for BER = $10^{-3}$ |

| Intermodulation rejection (1)                                                                                                            |     |                                  |     |                      | Wanted signal 3 dB above the sensitivity level, two CW jammers                                                                                                                                                                                                                                |

| 12.5 kHz channel spacing, 433 MHz                                                                                                        |     | 30                               |     | dB                   | at +2Ch and +4Ch where Ch is<br>channel spacing 12.5 kHz or 25                                                                                                                                                                                                                                |

| 25 kHz channel spacing, 868 MHz                                                                                                          |     | 30                               |     | dB                   | kHz. BER = 10 <sup>-2</sup>                                                                                                                                                                                                                                                                   |

| Parameter                                                                                             | Min | Тур                  | Max  | Unit         | Condition / Note                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------|-----|----------------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intermodulation rejection (2)<br>12.5 kHz channel spacing, 433 MHz<br>25 kHz channel spacing, 868 MHz |     | 56<br>55             |      | dB<br>dB     | Wanted signal 3 dB above the sensitivity level, two CW jammers at +10 MHz and +20 MHz offset.<br>BER = $10^{-2}$                                                         |

| LO leakage, 433/868 MHz                                                                               |     | <-80/-66             |      | dBm          |                                                                                                                                                                          |

| VCO leakage                                                                                           |     | -64                  |      | dBm          | VCO frequency resides between<br>1608 - 1880 MHz                                                                                                                         |

| Spurious emission, radiated CW<br>9 kHz - 1 GHz<br>1 - 4 GHz                                          |     | <-60<br><-60         |      | dBm<br>dBm   | Complying with EN 300 220,<br>FCC CFR47 part 15, ARIB STD-<br>T67, and ARIB STD-T96.<br>Spurious emissions can be<br>measured as EIRP values<br>according to EN 300 220. |

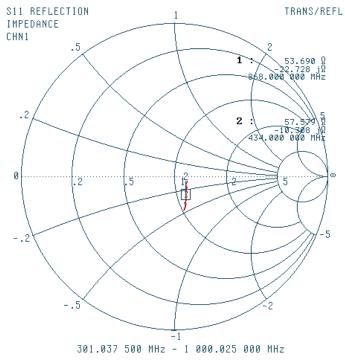

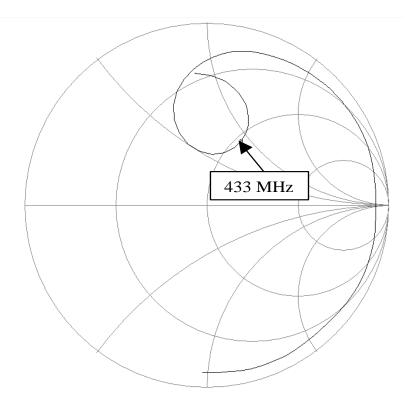

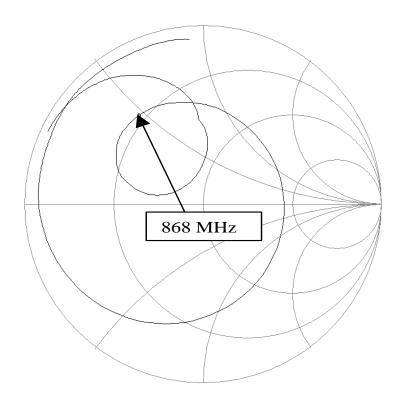

| Input impedance<br>433 MHz<br>868 MHz                                                                 |     | 58 - j10<br>54 - j22 |      | Ω<br>Ω       | Receive mode. See section 14 on page 46 for details.                                                                                                                     |

| Matched input impedance, S11<br>433 MHz<br>868 MHz                                                    |     | -14<br>-12           |      | dB<br>dB     | Using application circuit matching<br>network. See section 14 on page<br>46 for details.                                                                                 |

| Matched input impedance<br>433 MHz<br>868 MHz                                                         |     | 39 - j14<br>32 - j10 |      | Ω<br>Ω       | Using application circuit matching<br>network. See section 14 on page<br>46 for details.                                                                                 |

| Bit synchronization offset                                                                            |     |                      | 8000 | ppm          | The maximum bit rate offset<br>tolerated by the bit<br>synchronization circuit for 6 dB<br>degradation (synchronous modes<br>only)                                       |

| Data latency<br>NRZ mode<br>Manchester mode                                                           |     | 4<br>8               |      | Baud<br>Baud | Time from clocking the data on<br>the transmitter DIO pin until data<br>is available on receiver DIO pin                                                                 |

Table 4. RF receive parameters

# 4.3. RSSI / Carrier Sense Section

| Parameter                            | Min | Тур | Max | Unit | Condition / Note                                                                                                                                           |

|--------------------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSSI dynamic range                   |     | 55  |     | dB   | 12.5 and 25 kHz channel spacing                                                                                                                            |

| RSSI accuracy                        |     | ± 3 |     | dB   | See section 12.5 on page 33 for details.                                                                                                                   |

| RSSI linearity                       |     | ± 1 |     | dB   |                                                                                                                                                            |

| RSSI attach time                     |     |     |     |      | Shorter RSSI attach times can be traded for lower RSSI accuracy.                                                                                           |

| 2.4 kBaud, 12.5 kHz channel spacing  |     | 3.8 |     | ms   | See section 12.5 on page 33 for details.                                                                                                                   |

| 4.8 kBaud, 25 kHz channel spacing    |     | 1.9 |     | ms   | Shorter RSSI attach times can                                                                                                                              |

| 153.6 kBaud, 500 kHz channel spacing |     | 140 |     | μs   | also be traded for reduced<br>sensitivity and selectivity by<br>increasing the receiver channel<br>filter bandwidth.                                       |

| Carrier sense programmable range     |     | 40  |     | dB   | Accuracy is as for RSSI                                                                                                                                    |

| Adjacent channel carrier sense       |     |     |     |      | At corrier conce level 110 dBm                                                                                                                             |

| 12.5 kHz channel spacing             |     | -72 |     | dBm  | At carrier sense level –110 dBm,<br>FM jammer (1 kHz sine, ±2.5 kHz<br>deviation) at adjacent channel.                                                     |

| 25 kHz channel spacing               |     | -72 |     | dBm  | , ,                                                                                                                                                        |

|                                      |     |     |     |      | Adjacent channel carrier sense is<br>measured by applying a signal on<br>the adjacent channel and observe<br>at which level carrier sense is<br>indicated. |

| Spurious carrier sense               |     | -70 |     | dBm  | At carrier sense level –110 dBm,<br>100 MHz - 2 GHz. Adjacent<br>channel and image channel are<br>excluded.                                                |

| Table 5.      | RSSI/ | Carrier | sense  | parameters |

|---------------|-------|---------|--------|------------|

| 1 4 5 1 5 5 1 |       | •       | 001100 | parametere |

# 4.4. IF Section

| Parameter                        | Min | Тур                | Max | Unit | Condition / Note                                                                                                               |

|----------------------------------|-----|--------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------|

| Intermediate frequency (IF)      |     | 307.2              |     | kHz  | See section 12.1 on page 30 for details.                                                                                       |

| Digital channel filter bandwidth |     | 9.6<br>to<br>307.2 |     | kHz  | The channel filter 6 dB bandwidth<br>is programmable from 9.6 kHz to<br>307.2 kHz. See section 12.2 on<br>page 30 for details. |

| AFC resolution                   |     | 150                |     | Hz   | At 2.4 kBaud<br>Given as Baud rate/16. See<br>section 12.13 on page 41 for<br>details.                                         |

Table 6. IF section parameters

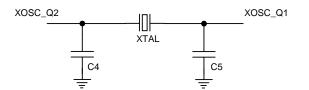

# 4.5. Crystal Oscillator Section

| Parameter                                                         | Min            | Тур                                         | Max            | Unit                             | Condition / Note                                                                                                                                                                                                      |

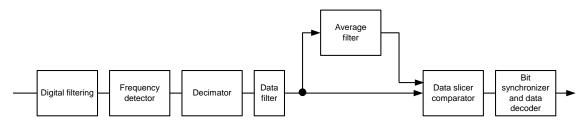

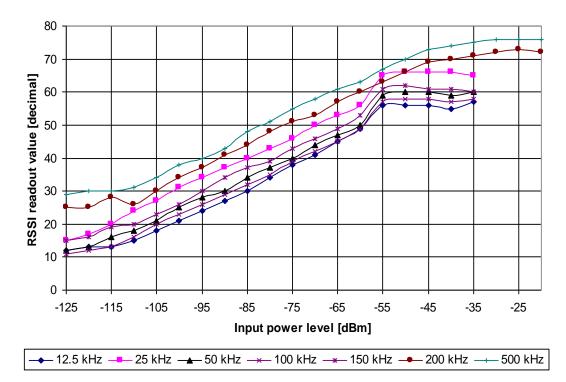

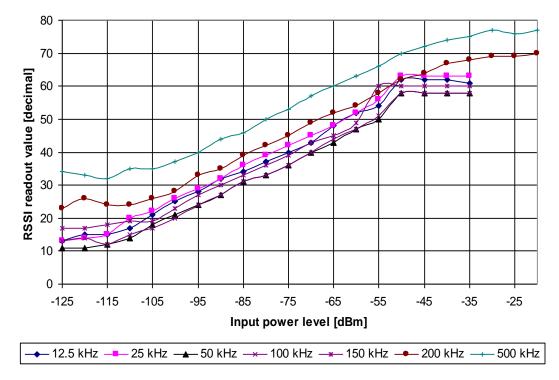

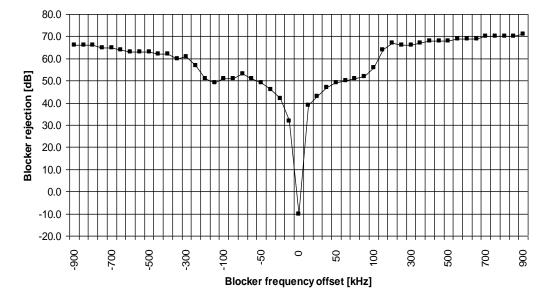

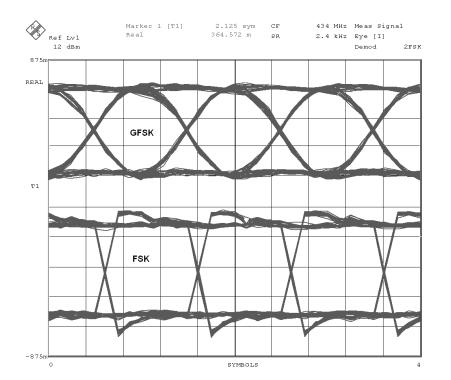

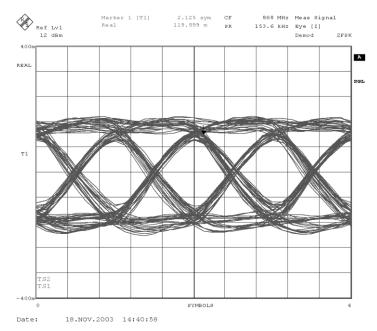

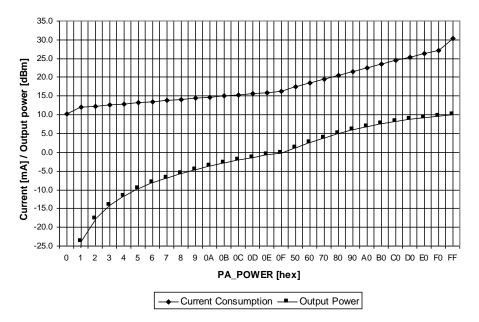

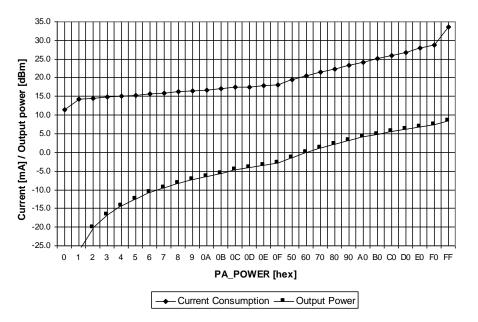

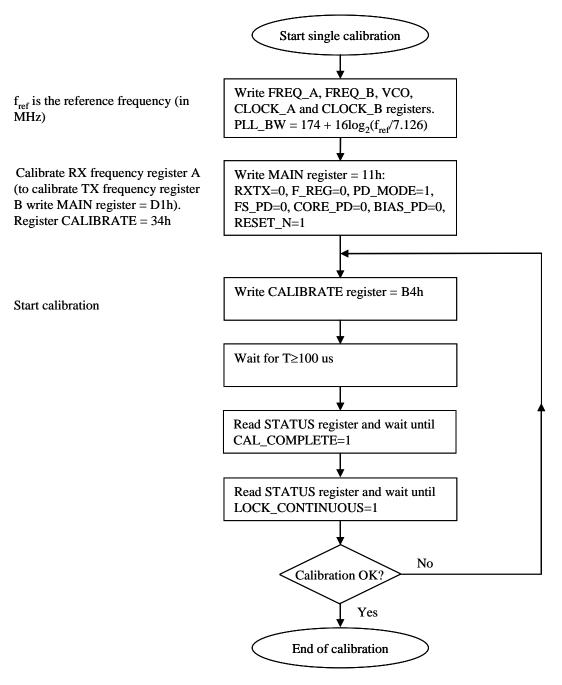

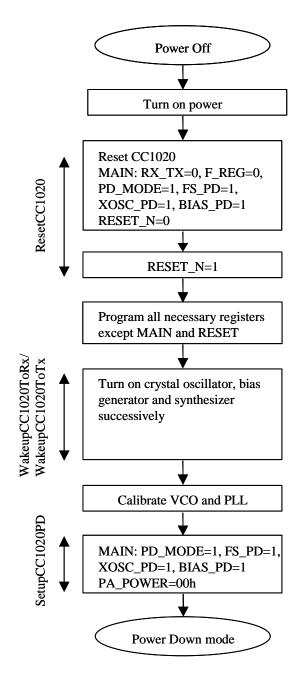

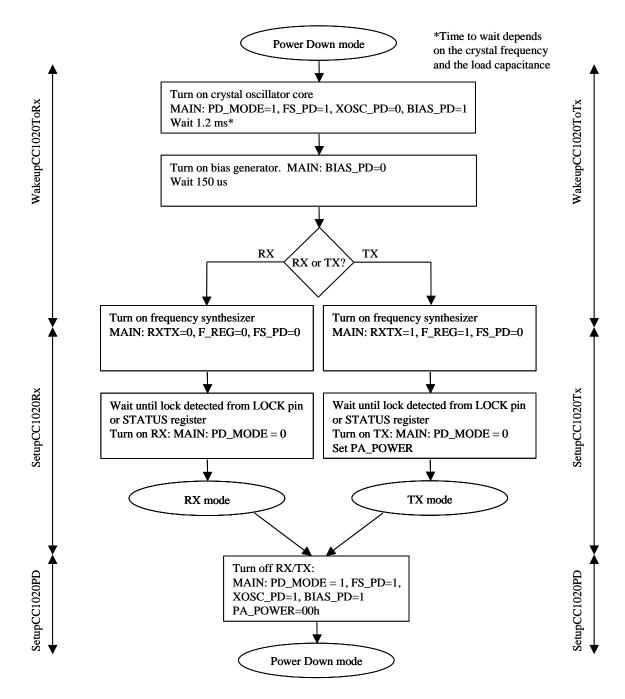

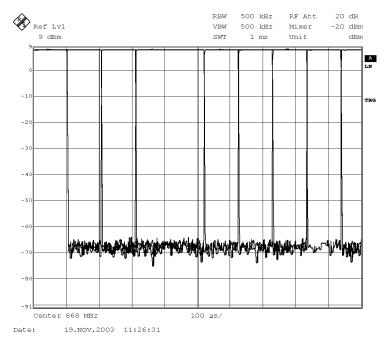

|-------------------------------------------------------------------|----------------|---------------------------------------------|----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|