June 2013

# FAH4820 Direct Driver for DC Motors (ERMs)

### **Features**

- Single-Pin Direct-Drive of ERM for Simple Vibration Control

- External Motor Enable/Disable, Vibration Control

- Register-Based I<sup>2</sup>C Control (Optional; Device Operates in Default Condition)

- Over-Driving Motor Control, Drive ERM Voltage to V<sub>DD</sub> Rail

- Programmable Motor Drive Voltage

- Low Standby Current: <1 µA</p>

- Fast Wake-up Time

- Nearly Rail-to-Rail Output Swing

- Protections: Under-Voltage, Over-Current, Over-Temperature

- Package: 10-Lead MLP

# **Applications**

- Mobile Phones

- Handheld Devices

- Keypad Interfaces

# **Description**

The FAH4820 is a high-performance enhanced ERM driver for mobile phone and other hand-held devices. This device does not require a PWM signal to generate vibration of the ERM; it is controlled by the drive level on the HEN input. The ERM spins for the length of time that the HEN pin is held HIGH, then stop when the HEN pin is pulled LOW. The FAH4820's register maps are accessible via I<sup>2</sup>C serial communication, which is useful for higher or lower drive voltage across the ERM or if disabling the device is desired.

### **Related Resources**

AN-5067 — PCB Land Pattern Design and Surface-Mount Guidelines for MLP Packages

# Ordering Information

| Part Number | Operating<br>Temperature Range | Package                                                                    | Packing Method               |

|-------------|--------------------------------|----------------------------------------------------------------------------|------------------------------|

| FAH4820MPX  | -40°C to +85°C                 | 10-Lead, Dual, JEDEC MO-229, 3 mm Square,<br>Molded Leadless Package (MLP) | 3000 Units on<br>Tape & Reel |

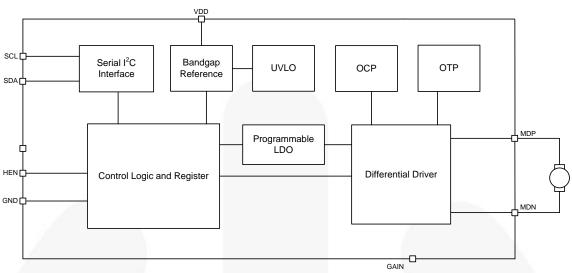

# **Block Diagram**

Figure 1. Block Diagram

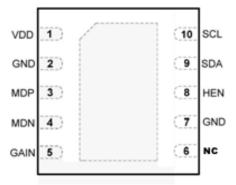

# **Pin Configuration**

Figure 2. Pin Assignments

### **Pin Definitions**

| Name | Pin# | Туре   | Description                                       |

|------|------|--------|---------------------------------------------------|

| VDD  | 1    | Power  | Power                                             |

| GND  | 2, 7 | Power  | Ground                                            |

| MDP  | 3    | Output | Positive motor driver output                      |

| MDN  | 4    | Output | Negative motor driver output                      |

| GAIN | 5    | Input  | Gain control for motor driving                    |

| NC   | 6    | NA     | No connection                                     |

| HEN  | 8    | Input  | Motor enable/disable (HIGH: enable, LOW: disable) |

| SDA  | 9    | Input  | I <sup>2</sup> C data input                       |

| SCL  | 10   | Input  | I <sup>2</sup> C clock input                      |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol          | Parameter                                          | Min. | Max.                 | Unit |

|-----------------|----------------------------------------------------|------|----------------------|------|

| $V_{DD}$        | DC Supply Voltage                                  | -0.3 | 6.0                  | V    |

| V <sub>IO</sub> | Analog and Digital I/O (All Input and Output Pins) | -0.3 | V <sub>CC</sub> +0.3 | V    |

# **Reliability Information**

| Symbol           | Parameter                                                              | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------------------------------------|------|------|------|------|

| TJ               | Junction Temperature                                                   |      |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                              | -65  |      | +150 | °C   |

| $\Theta_{JA}$    | Thermal Resistance, JEDEC Standard, Multi-Layer Test Boards, Still Air |      | 200  |      | °C/W |

# **Electrostatic Discharge Information**

| Symbol | Parameter                         | Max. | Unit |

|--------|-----------------------------------|------|------|

| ESD    | Human Body Model, JESD22-A114     | ±4   | kV   |

|        | Charged Device Model, JESD22-C101 | ±1   | KV   |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                   | Min. | Тур. | Max. | Unit |

|----------------|-----------------------------|------|------|------|------|

| T <sub>A</sub> | Operating Temperature Range |      |      | +85  | Ç    |

| $V_{DD}$       | Supply Voltage Range        | 2.7  | 3.3  | 5.5  | V    |

# **DC Electrical Characteristics**

$T_A = 25$ °C,  $V_{DD} = 3.3$  V, and  $V_{LDO} = 3.0$  V unless otherwise noted.

| Symbol             | Parameter                    | Conditions                                                             | Min.                  | Тур. | Max.                  | Unit |

|--------------------|------------------------------|------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| IIH <sub>HEN</sub> | Input Current                | HEN = 3.3 V                                                            |                       | 1    | 2                     | μA   |

| IIL <sub>HEN</sub> | Input Current                | HEN = 0.0 V                                                            |                       | 1    | 2                     | μA   |

| IIH <sub>SCL</sub> | Input Current                | SCL = 3.3 V                                                            |                       | 0    | 1                     | μA   |

| IIH <sub>SDA</sub> | Input Current                | SDA = 3.3 V                                                            |                       | 0    | 1                     | μA   |

| IIL <sub>SCL</sub> | Input Current                | SCL = 0.0 V                                                            |                       | 0    | 1                     | μA   |

| IIL <sub>SDA</sub> | Input Current                | SDA = 0.0 V                                                            |                       | 0    | 1                     | μA   |

| V <sub>IH</sub>    | Input Logic HIGH             |                                                                        | 0.7 X V <sub>DD</sub> |      |                       | V    |

| V <sub>IL</sub>    | Input Logic LOW              |                                                                        |                       |      | 0.3 X V <sub>DD</sub> | V    |

| V <sub>OL</sub>    | Output Voltage               | $V_{DD} = 3.3 \text{ V}, R_L = 10 \Omega$                              |                       | 100  | 200                   | mV   |

| V <sub>OH</sub>    | Output Voltage               | $V_{DD} = 3.3 \text{ V}, R_L = 10 \Omega$                              | V <sub>LDO</sub> -0.3 |      |                       | V    |

| l <sub>out</sub>   | Short-Circuit<br>Protection  | V <sub>DD</sub> = 3.3 V, MDP to MDN Short to Each Other & Short to GND |                       | 500  |                       | mA   |

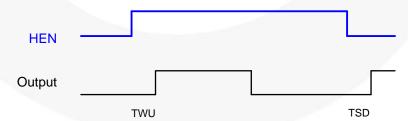

| t <sub>WU</sub>    | Wake-up Time                 |                                                                        |                       | 50   | 150                   | μs   |

| t <sub>SD</sub>    | Shutdown Time                | HEN HIGH to LOW                                                        |                       | 1    | 150                   | μs   |

| R <sub>IN</sub>    | Input Resistance             | Gain Input – Default Register<br>Setting                               |                       | 10   |                       | kΩ   |

| C <sub>IN</sub>    | Input Capacitance            | Gain Input                                                             |                       | 10   |                       | pF   |

| I <sub>DD1</sub>   | Supply Current               | R <sub>L</sub> = No Load, HEN=LOW                                      |                       | 10   | 20                    | μΑ   |

| I <sub>DD2</sub>   | Supply Current               | R <sub>L</sub> = No Load, HEN=HIGH                                     |                       | 2.5  | 5.0                   | mA   |

| I <sub>DD3</sub>   | Supply Current               | $R_L$ = 10 Ω, HEN=HIGH                                                 |                       | 275  |                       | mA   |

| I <sub>PD</sub>    | Power-Down Supply<br>Current | V <sub>DD</sub> = 2.7 V, V <sub>LDO</sub> = 2.4 V,<br>Reg 0x20 Bit 7=0 |                       | 20   | 50                    | nA   |

| V <sub>OUT</sub>   | Output Voltage<br>Range      |                                                                        | 2.4                   | 3.0  | 3.6                   | V    |

| $V_{REG}$          | Output Voltage<br>Accuracy   |                                                                        | -10                   |      | 10                    | %    |

Figure 3. Enable/Disable Functional Timing

# I<sup>2</sup>C DC Electrical Characteristics

$T_A = 25$ °C,  $V_{DD} = 3.3$  V, and  $V_{LDO} = 3.0$  V unless otherwise noted.

| Cumbal          | Davamatav                                                                    | Fast Mode (400 kHz)           Min.         Max.         Uni           -0.3         0.6         V           1.3         V | kHz) |      |

|-----------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|

| Symbol          | Parameter                                                                    | Min.                                                                                                                     | Max. | Unit |

| V <sub>IL</sub> | Low-Level Input Voltage                                                      | -0.3                                                                                                                     | 0.6  | V    |

| V <sub>IH</sub> | High-Level Input Voltage                                                     | 1.3                                                                                                                      |      | V    |

| V <sub>OL</sub> | Low-Level Output Voltage at 3 mA Sink Current (Open-Drain or Open-Collector) | 0                                                                                                                        | 0.4  | V    |

| l <sub>IH</sub> | High-Level Input Current of Each I/O Pin, Input Voltage = V <sub>DD</sub>    | -1                                                                                                                       | 1    | μΑ   |

| I <sub>IL</sub> | Low-Level Input Current of Each I/O Pin, Input Voltage = 0 V                 | -1                                                                                                                       | 1    | μΑ   |

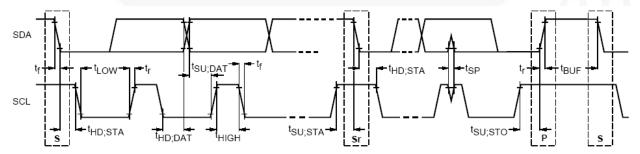

## I<sup>2</sup>C AC Electrical Characteristics

| Cumbal              | Develope                                                          | Fast                 | Fast Mode (400 kHz)                            |     |

|---------------------|-------------------------------------------------------------------|----------------------|------------------------------------------------|-----|

| Symbol              | Parameter                                                         | Min.                 | Max. Unit 400 kHz μs μs μs μs ο.9 μs ns 300 ns |     |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0                    | 400                                            | kHz |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                  |                                                | μs  |

| $t_{LOW}$           | Low Period of SCL Clock                                           | 1.3                  |                                                | μs  |

| t <sub>HIGH</sub>   | High Period of SCL Clock                                          | 0.6                  |                                                | μs  |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition                          | 0.6                  |                                                | μs  |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0                    | 0.9                                            | μs  |

| t <sub>SU;DAT</sub> | Data Set-up Time <sup>(1)</sup>                                   | 100                  |                                                | ns  |

| t <sub>r</sub>      | Rise Time of SDA and SCL Signals <sup>(2)</sup>                   | 20+0.1C <sub>b</sub> | 300                                            | ns  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(2)</sup>                   | 20+0.1C <sub>b</sub> | 300                                            | ns  |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                    | 0.6                  |                                                | μs  |

| t <sub>BUF</sub>    | Bus-Free Time between STOP and START Conditions                   | 1.3                  |                                                | μs  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                    | 50                                             | ns  |

### Notes:

- 1. A Fast-Mode I²C Bus® device can be used in a Standard-Mode I²C bus system, but the requirement t<sub>SU;DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the Serial Data (SDA) line t<sub>r\_max</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-Mode I²C Bus specification) before the SCL line is released.

- 2. C<sub>b</sub> equals the total capacitance of one bus line in pf. If mixed with High-Speed Mode devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

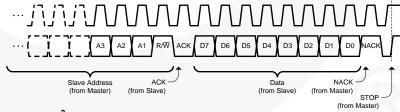

Figure 4. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus

# **Functional Description**

### I<sup>2</sup>C Control

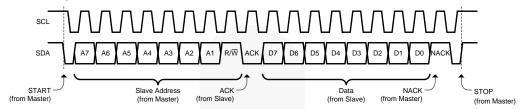

Writing to and reading from registers is accomplished via the I<sup>2</sup>C interface. The I<sup>2</sup>C protocol requires that one device on the bus initiates and controls all read and write operations. This device is called the "master" device. The master device generates the SCL signal, which is the clock signal for all other devices on the bus. All other devices on the bus are called "slave" devices. The FAH4820 is a slave device. Both the master and slave devices can send and receive data on the bus.

During I<sup>2</sup>C operations, one data bit is transmitted per clock cycle. All I<sup>2</sup>C operations follow a repeating nine-clock-cycle pattern that consists of eight bits (one byte) of transmitted data followed by an acknowledge (ACK) or not acknowledge (NACK) from the receiving device. Note that there are no unused clock cycles during any operation; therefore, there must be no breaks in the stream of data and ACKs/NACKs during data transfers.

For most operations, I<sup>2</sup>C protocol requires the SDA line remain stable (unmoving) whenever SCL is HIGH. For example, transitions on the SDA line can only occur when SCL is LOW. The exceptions are when the master device issues a START or STOP condition. The slave device cannot issue a START or STOP condition.

**START Condition:** This condition occurs when the SDA line transitions from HIGH to LOW while SCL is HIGH. The master device uses this condition to indicate that a data transfer is about to begin.

**STOP Condition:** This condition occurs when the SDA line transitions from LOW to HIGH while SCL is HIGH. The master device uses this condition to signal the end of a data transfer.

**Acknowledge and Not Acknowledge:** When data is transferred to the slave device, the slave device sends acknowledge (ACK) after receiving every byte of data. The receiving device sends an ACK by pulling SDA LOW for one clock cycle.

When the master device is reading data from the slave device, the master sends an ACK after receiving every byte of data. Following the last byte, a master device sends a "not acknowledge" (NACK) instead of an ACK, followed by a STOP condition. A NACK is indicated by leaving SDA HIGH during the clock after the last byte.

### **Slave Address**

Each slave device on the bus must have a unique address so the master can identify which device is sending or receiving data. The FAH4820 slave address is 0000110X binary, where "X" is the read/write bit. Master write operations are indicated when X=0. Master read operations are indicated when X=1.

### Writing to and Reading from the FAH4820

All read and write operations must begin with a START condition generated by the master. After the START condition, the master must immediately send a slave address (7 bits), followed by a read/write bit. If the slave address matches the address of the FAH4820, the

FAH4820 sends an ACK after receiving the read/write bit by pulling the SDA line LOW for one clock cycle.

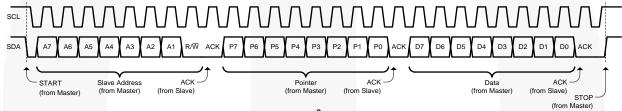

### **Setting the Pointer**

For all operations, a "pointer" stored in the command register must be indicating the register to be written or read. To change the pointer value in the command register, the read/write bit following the address must be 0. This indicates that the master writes new information into the command register.

After the FAH4820 sends an ACK in response to receiving the address and read/write bit, the master must transmit an appropriate 8-bit pointer value, as explained in the I<sup>2</sup>C Registers section. The FAH4820 sends an ACK after receiving the new pointer data.

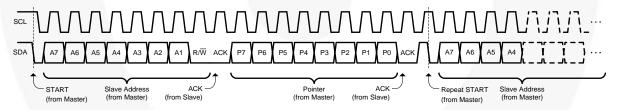

The pointer-set operation is illustrated in Figure 7 and Figure 8. Any time a pointer-set is performed, it must be immediately followed by a read or write operation. The command register retains the pointer between operations; once a register is indicated, subsequent read operations do not require a pointer set cycle. Write operations always require the pointer be reset.

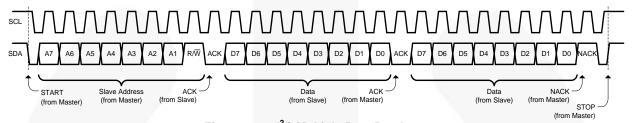

### Reading

If the pointer is already pointing to the desired register, the master can read from that register by setting the read/write bit (following the slave address) to 1. After sending an ACK, the FAH4820 begins transmitting data during the following clock cycle. The master should respond with a NACK, followed by a STOP condition (see Figure 5).

The master can read multiple bytes by responding to the data with an ACK instead of a NACK and continuing to send SCL pulses, as shown in Figure 6. The FAH4820 increments the pointer by one and sends the data from the next register. The master indicates the last data byte by responding with a NACK, followed by a STOP.

To read from a register other than the one currently indicated by the command register, a pointer to the desired register must be set. Immediately following the pointer-set, the master must perform a REPEAT START condition (see Figure 8), which indicates to the FAH4820 that a new operation is about to occur. If the REPEAT START condition does not occur, the FAH4820 assumes that a write is taking place and the selected register is overwritten by the upcoming data on the data bus. After the START condition, the master must again send the device address and read/write bit. This time, the read/write bit must be set to 1 to indicate a read. The rest of the read cycle is the same as described for reading from a preset pointer location.

#### Writing

All writes must be preceded by a pointer set, even if the pointer is already pointing to the desired register.

Immediately following the pointer-set, the master must begin transmitting the data to be written. After transmitting each byte of data, the master must release the Serial Data (SDA) line for one clock cycle to allow the FAH4820 to acknowledge receiving the byte. The write operation should be terminated by a STOP condition from the master (see Figure 7).

As with reading, the master can write multiple bytes by continuing to send data. The FAH4820 increments the

pointer by one and accepts data for the next register. The master indicates the last data byte by issuing a STOP condition.

### **Read / Write Diagrams**

Figure 5. I<sup>2</sup>C Read

Figure 6. I<sup>2</sup>C Multiple Byte Read

Figure 7. I<sup>2</sup>C Write

Figure 8. I<sup>2</sup>C Write Followed by Read

### **Digital Interface**

The I<sup>2</sup>C-compatible interface is used to program the FAH4820 as listed in the below register configurations. The I<sup>2</sup>C address of the FAH4820 is 0x06.

| Binary   | Hex  |

|----------|------|

| 00000110 | 0x06 |

# **Register Definitions**

Table 1. Control Registers and Default Values

| Address | Address Register Name |     | Reset Value |

|---------|-----------------------|-----|-------------|

| 0x20    | CONTROL0              | R/W | 10010000    |

| 0x21    | CONTROL1              | R/W | 00101100    |

| 0x22    | STAT                  | R   | 00001110    |

### Table 2. Control Register MAP (Control0, Control1, Status)

| Bit7 | Bit6             | Bit5       | Bit4        | Bit3 | Bit2     | Bit1  | Bit0     |

|------|------------------|------------|-------------|------|----------|-------|----------|

| En   | ODRV_EN          | ODRVEN_HL  |             |      | Reserved |       |          |

|      | Input Resistance | [7:5]      | VLDO_OUT    |      | Rese     | erved |          |

|      | Rese             | erved[7:4] | VDD_G VREG_ |      | VREG_G   | OT    | Reserved |

### Notes:

3. Connect the bottom DAP to ground.

### Table 3. Control 0

Address: 20h

Reset Value: 1001\_0000

■ Type: Read/Write

■ **BOLD** is default state

| Bit # | Name      | Size (Bits) | Description                                                                                        |  |

|-------|-----------|-------------|----------------------------------------------------------------------------------------------------|--|

| 7     | En        | 1           | Drive Enable Mode 0: Power-Down Mode 1: Normal Operation Mode                                      |  |

| 6     | ODRV_EN   | 1           | Over-Drive Enable Mode  0: Disable Over Drive  1: Enable Over Drive                                |  |

| 5     | ODRVEN_HL | 1           | Selection of Over-Drive  0: Over-Drive LOW (MDN to VDD RAIL)  1: Over-Drive HIGH (MDP TO VDD RAIL) |  |

| 4     | Reserved  | 1           | Not used                                                                                           |  |

| 3:2   | Reserved  | 2           | Not used                                                                                           |  |

| 1:0   | Reserved  | 2           | Not used                                                                                           |  |

### Table 4. Control 1

Address: 21h

Reset Value: 0010\_1100

Type: Read/WriteBOLD is default state

| Bit# | Name             | Size (Bits) |                                                                                                                    | Description |

|------|------------------|-------------|--------------------------------------------------------------------------------------------------------------------|-------------|

| 7:5  | Input Resistance | 3           | 000: 8 kΩ<br><b>001: 10 kΩ</b><br>010: 12 kΩ<br>011: 14 kΩ<br>100: 16 kΩ<br>101: 18 kΩ<br>110: 20 kΩ<br>111: 22 kΩ |             |

| 4:2  | VLDO_OUT         | 3           | 000: 2.4 V<br>001: 2.6 V<br>010: 2.8 V<br><b>011: 3.0 V</b><br>100: 3.2 V<br>101 :3.4 V<br>110: 3.6 V              |             |

| 1:0  | Reserved         | 2           | Not used                                                                                                           |             |

### Table 5. Status

Address: 22h

Reset Value: 0000\_1110

■ Type: Read Only

| Bit # | Name       | Size (Bits) | Description                                                                                                                                  |  |

|-------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:4   | Reserved   | 4           | Not used                                                                                                                                     |  |

| 3     | VDD_G      | 1           | 0: Input voltage is not valid (under UVLO); input voltage is less than 2.3 (rising) / 2.1 V (falling)  1: Input voltage is valid (over UVLO) |  |

| 2     | VLDO_OUT_G | 1           | 0: Regulator output is not valid (V <sub>LDO_OUT</sub> is less than 70% of V <sub>LDO_OUT</sub> programmed)  1: Regulator output is valid    |  |

| 1     | ОТ         | 1           | O: Over-temperature protection is tripped     Cover-temperature protection is not tripped                                                    |  |

| 0     | Reserved   | 1           | Not used, default is 0                                                                                                                       |  |

Table 6.  $V_{DD}$  vs.  $V_{LDO\_OUT}$

|                       | V <sub>DD</sub> (V) |     |     |     |     |     |

|-----------------------|---------------------|-----|-----|-----|-----|-----|

|                       | 2.7                 | 3.0 | 3.3 | 4.5 | 5.0 | 5.5 |

|                       | 2.4                 | 2.4 | 2.4 | 2.4 | 2.4 | 2.4 |

| $V_{LDO\_OUT}$        | 2.6                 | 2.6 | 2.6 | 2.6 | 2.6 | 2.6 |

| (Programmed Voltage)  |                     | 2.8 | 2.8 | 2.8 | 2.8 | 2.8 |

| (i rogrammed voltage) |                     |     | 3.0 | 3.0 | 3.0 | 3.0 |

|                       |                     |     | 3.2 | 3.2 | 3.2 | 3.2 |

|                       |                     |     |     | 3.4 | 3.4 | 3.4 |

|                       |                     |     |     | 3.6 | 3.6 | 3.6 |

# **Applications Information**

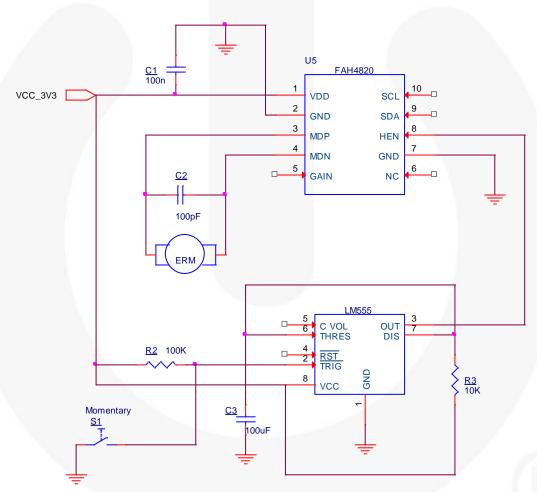

Many of the FAH4820 functions can be controlled through the  $I^2C$  interface, but this application demonstrates the device in default state when powered up. In the default state; the device is enabled, overdrive is disabled, input resistance is  $10\,k\Omega,$  and the differential drive voltage is set to 3.0 V. The device design allows the user to leave the SCL and SDA line floating. The differential outputs are held at ground until the HEN pin is pulled HIGH, which causes the ERM to rotate until the HEN signal is pulled LOW or a timer circuit pulls the HEN signal LOW. Figure 9 shows an example using a 555 timer to control a single vibration

from an ERM. The length of time the ERM is rotating is determined by the RC time constant of R3 and C3. In this case, the motor rotate for 1.1 second every time the button is pressed. Electromagnetic Interference (EMI) is the radiation of electromagnetic noise. This noise can affect control signals and other electronics, which can produce errors and reduce performance. The DC motors used in ERMs are a common source of EMI due to commutator arcing. It is recommended that a 100 pF capacitor be placed across the MDP and MPN pins. In this case, this is C2, which greatly reduces EMI produced by the ERM.

Figure 9. 555 Timer Control of Single Vibration from ERM

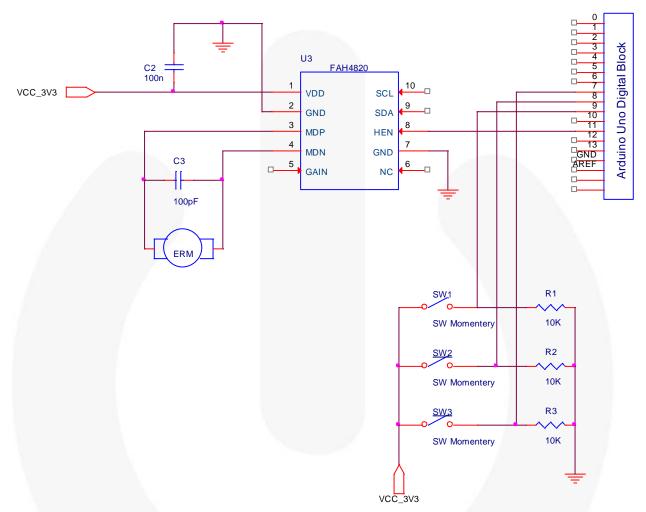

Figure 10 is an example of using Arduino Uno to control the HEN pin based on which of the three switches is pressed. In the example program below; when SW1 is pressed (which is connected to Arduino input pin 10), the ERM spins once for the length of time the program holds pin 12 HIGH. The other switches produce a

double pulse (SW2) and a triple pulse (SW3) output. Due to EMI noise, it is recommended that a 100 pF capacitor be placed across the MDP and MPN pins. In this case, this is C3, which greatly reduces EMI produced by the ERM.

Figure 10. Arduino Uno Control HEN Pin

### **Vibration Alert Arduino Example Program**

```

/* FAH4820 vibration alert Arduino program*/

int VIBpin = 12;

int switchPin = 8;

int switchPin1 = 9;

int switchPin2 = 10;

void setup()

{

pinMode(VIBpin, OUTPUT);

pinMode(switchPin, INPUT);

pinMode(switchPin1, INPUT);

pinMode(switchPin2, INPUT);

}

void loop()

{

if (digitalRead(switchPin) == HIGH) /* run this sequence if pin 8 is high - triple

pulse*/

{

}

```

```

digitalWrite(VIBpin, HIGH);

delay(600);

digitalWrite(VIBpin, LOW);

delay(300);

digitalWrite(VIBpin, HIGH);

delay(300);

digitalWrite(VIBpin,LOW);

delay(300);

digitalWrite(VIBpin, HIGH);

delay(150);

digitalWrite(VIBpin,LOW);

delay(300);

else

digitalWrite(VIBpin,LOW);

if (digitalRead(switchPin1) == HIGH) /* run this sequence if pin 9 is high - double

pulse*/

digitalWrite(VIBpin, HIGH);

delay(600);

digitalWrite(VIBpin,LOW);

delay(300);

digitalWrite (VIBpin, HIGH);

delay(150);

digitalWrite(VIBpin,LOW);

delay(300);

else

digitalWrite (VIBpin, LOW);

if (digitalRead(switchPin2) == HIGH) /* run this sequence if pin 10 is high -

single pulse*/

digitalWrite(VIBpin, HIGH);

delay(600);

digitalWrite (VIBpin, LOW);

delay(300);

else

digitalWrite (VIBpin, LOW);

```

### Internal LDO

The internal LDO is designed for an I<sup>2</sup>C seven-step adjustable output voltage. This provides flexibility for various motor voltages and configurations for low-power consumption. The LDO includes an internal circuit for short-circuit current protection.

### Serial Interface

On power-up, the device default values are invoked. The FAH4820 allows programming through the registers: the VLDO out, over drive, power down, and others functions. The device functions without any I<sup>2</sup>C input signals connected.

### **Thermal Shutdown**

If the junction temperature is above 150°C, the temperature control block shuts down and stays off until the temperature is below 134°C. The register values are kept as written so that it's not required to initialize again.

### **Over-Current Limitation**

The driver includes a current-limitation block to protect against an over-current condition, mainly caused by a

stuck-rotor condition. Over-current protection limitation is 500 mA, typical.

### **Over-Drive Motor Control**

A common approach to driving DC motors is to over-drive a voltage that overcomes the inertia of the motor's mass. The motor is often overdriven for a short time before returning to the rated voltage to sustain rotation. The FAN4820 block can over-drive a motor up to the  $V_{\text{DD}}$  voltage.

### **Over-Drive Duration**

It is important that over-drive time not damage the motor. The over-drive duration must be dependent on the motor datasheet and care must be taken not to assert an over-voltage condition over the rated time limit of the motor.

### Status Registers

The FAH4820 has a status register set that monitors LDO input voltage, regulator output voltage, and over-temperature status.

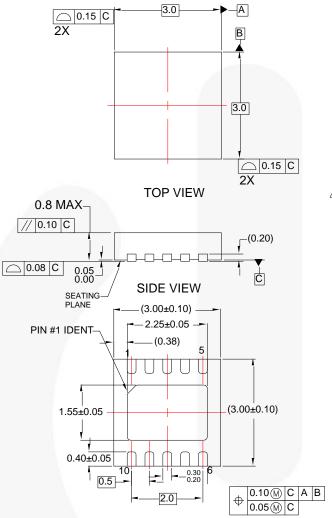

# **Physical Dimensions**

0.23 - 0.02 - 0.50 - 0.25

RECOMMENDED LAND PATTERN

**BOTTOM VIEW**

### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-229, VARIATION WEED-5

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER

ASME Y14.5M, 1994

(À) LAND PATTERN DIMENSIONS ARE NOMINAL REFERENCE VALUES ONLY

MLP10BrevA

Figure 11. 10-Lead, JEDEC MO-229, 3 mm Square, Molded Leadless Package (MLP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

**FPS™** AccuPower™ AX-CAP®\* F-PFS™ FRFET® BitSiC™ Global Power Resource Build it Now™ GreenBridge™ CorePLUS™ Green FPS™ Green FPS™ e-Series™ CorePOWER™ Gmax™ CROSSVOLTTM CTL™ GTO™

IntelliMAX™ Current Transfer Logic™ ISOPLANAR™ **DEUXPEED®**

Dual Cool™ Making Small Speakers Sound Louder and Better™

MegaBuck™

MicroFET<sup>TM</sup>

MicroPak™

MicroPak2™

MillerDrive™

MotionMax™

mWSaver™

OptoHiT™

OPTOLOGIC<sup>®</sup>

OPTOPLANAR®

EcoSPARK® EfficientMax™ MICROCOUPLER™ ESBC™

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT® FAST®

FastvCore™ FETBench™ PowerTrench® PowerXS™

Programmable Active Droop™ **QFET**

OS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™ SignalWise™

SMART START™ Solutions for Your Success™ SPM®

SmartMax™

STEALTH\* SuperFET<sup>®</sup> SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™

Sync-Lock™ SYSTEM SYSTEM

TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ TranSiC™ TriFault Detect™ TRUECURRENT®\* uSerDes™

UHC® Ultra FRFET™ UniFET™ VCX<sup>™</sup> VisualMax™ VoltagePlus™ XSTM

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

### **Definition of Terms**

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.  The datasheet is for reference information only.                                                   |

|                          |                       | D.:: 104                                                                                                                                                                                            |

Rev. 164